Hi,

ds90ub948 mention duty cycle ratio of 57:43.

could you help give the detail for 57 and 43 come from?

best regards,

jeff wang

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

Hi,

ds90ub948 mention duty cycle ratio of 57:43.

could you help give the detail for 57 and 43 come from?

best regards,

jeff wang

Hello Jeff,

can you provide more details? Duty cycle for what? where is that info written?

Hi,

you can search in datasheet:

7.4.1.1 1-Lane FPD-Link III Input, Single Link OpenLDI Output

In this configuration the PCLK rate embedded within the 1-lane FPD-Link III frame can range from 25 MHz to 96

MHz, resulting in a link rate of 875 Mbps (35 bit × 25 MHz) to 3.36 Gbps (35 bit × 96 MHz). Each LVDS data lane

operates at a speed of 7 bits per LVDS clock cycle; resulting in a serial line rate of 175 Mbps to 672 Mbps. CLK1

operates at the same rate as PCLK with a duty cycle ratio of 57:43.

Hi Jeff,

You can find some clarification in the datasheet section 7.4.3.

The LVDS clock output from CLK1± and CLK2± follows a 4:3 duty cycle scheme, with each 28-bit pixel frame starting with two LVDS bit clock periods high, three low, and ending with two high.

Hi Jaradat,

sorry, form that describe, I still cannot get 57 and 43.

clk1,clk2 follows a 4:3 duty cycle scheme, how to get 57 and 43?

57 stand for what?

43 stand for what?

best regards,

jeff wang

Hello Jeff,

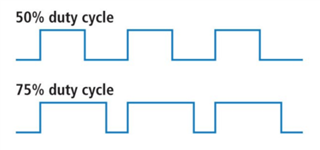

57% : 43% is the ratio of high and low in duty cycle. If you divide 100% by 7 you will get ~14.3% . 4:3 = 4x14.3 : 3x14.3 = 57:43.