Part Number: DP83867CS

Dear support team,

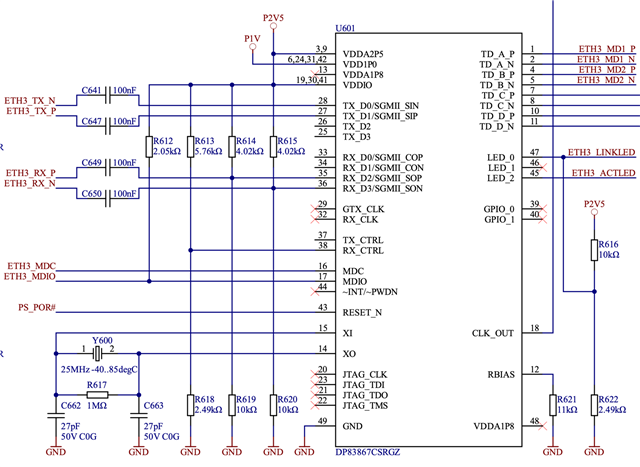

we determined a functional failure after reset. It is assumed that the RESET_N input of the IC with a newer batch of DP83867CS casing the problem. The reset signal is connected to a capacitor to make it more robust against disturbances, so the signal has a slowly rising edge. With the old revision (see image) the edge has a tau of 1ms and there has never been a problem with the reset, the tau can even be increased to 100ms and there have never be experienced a problem after a reset.

We had to reduce the tau to 100us with a newer revision (see image) and in 2% of cases there is still a problem with the reset. It seems that the IC is not initialized correctly after the reset and the chip is not working. With a tau of 100ms the IC does not work after every reset and cannot be operated.

The question for us now is whether a certain requirement is imposed on the RESET_N signal. Is it possible that a Schmitt trigger must be used? Unfortunately, we could not find a specification for this in the data sheet.

Thanks,

Patrick