Part Number: DS90UB948-Q1

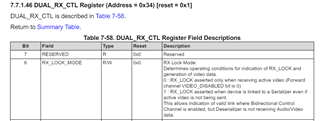

We are using 948 and 949, currently the LOCK signal of 948 is low, may I ask if the CLOCK signal of 948 can also be set high as long as the three pins of MODE_SEL0, MODE_SEL1 and MODE_SEL2 are correctly configured on the hardware and the other registers are not configured?Is there anything on the schematic that needs attention? LOCK is always low, may I ask what causes it?