Topic linked to Thread ID: 1345118

Could customer lower clocks and or rise and fall times with UB913/4 to ease PCB routing and EMC probation?

If so please share which register settings influence this.

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

Topic linked to Thread ID: 1345118

Could customer lower clocks and or rise and fall times with UB913/4 to ease PCB routing and EMC probation?

If so please share which register settings influence this.

Hi Frank,

Could you elaborate which signals you are referring to here? In the case of the UB913 & UB914 we should focus first on following PCB routing best practices to prevent EMC issues.

Best,

Thomas

Hi Thomas,

Their data rate is very low, I2C is the fasters interface they transfer over FPD-link. So every clock or data transmission that could be reduced will help them ease EMC.

Of course lay-out is important but knowing that they want to achieve up to 10mtrs over LAN cable, lowering the data rate (and flanks) will help them on EMC level.

Hi Frank,

The data rate from an FPD-Link perspective is determined by the PCLK of the imager being used. In order to reduce the frequency of the line rate, the imager throughput would need to be reduced as well.

For the rise and fall times pertaining to the 913 device, this would be the PCLK signal and I2C.

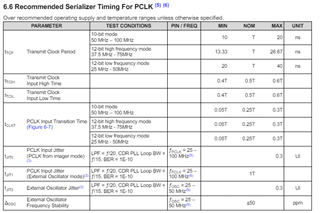

For the PCLK signal, the following specifications must be followed:

The maximum input transition time for the PCLK signal is 0.3T where T is the transmit clock period.

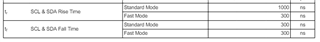

I2C rise and fall times for the devices have the following maximum timings:

Best,

Zoe