I have a board with a TCAN4550-Q1 component, connected to a 40 MHz Crystal

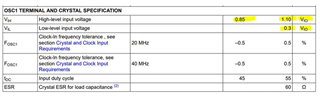

During testing, I saw in DS that the OSC1 Terminal requires the input level as follows (marked in yellow):

What does this requirement mean?

What are the units VIO?

For example, I have the following signal (attached Pic) I have measured in the OSC1 terminal:

VIH= 1.204V

VIL= 0.564V

Does this signal meet the requirement from the table?