Part Number: TLIN1431-Q1

I am using the TLIN1431 well, but after shorting VCC 3.3V and GND, the SBC (TLIN1431) continues to generate a reset signal, so the MCU is not working.

But when I do power on reset, it works fine.

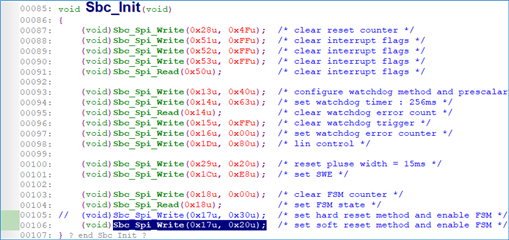

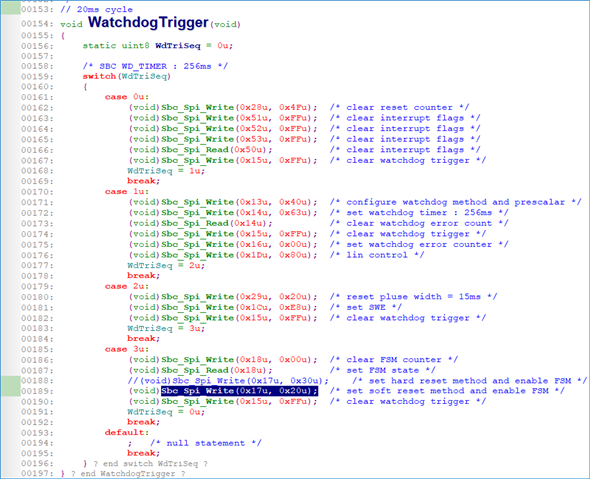

What do you need to add to the initialisation code below?

//SBC init fuction//

(void)Sbc_Spi_Write(0x28u, 0x4Fu); /* clear reset counter */

(void)Sbc_Spi_Write(0x51u, 0xFFu); /* clear interrupt flags */

(void)Sbc_Spi_Write(0x52u, 0xFFu); /* clear interrupt flags */

(void)Sbc_Spi_Write(0x53u, 0xFFu); /* clear interrupt flags */

(void)Sbc_Spi_Read(0x50u); /* clear interrupt flags */

(void)Sbc_Spi_Write(0x13u, 0x40u); /* configure watchdog method and prescalar */

(void)Sbc_Spi_Write(0x14u, 0x63u); /* set watchdog timer : 256ms */

(void)Sbc_Spi_Read(0x14u); /* clear watchdog error count */

(void)Sbc_Spi_Write(0x15u, 0xFFu); /* clear watchdog trigger */

(void)Sbc_Spi_Write(0x16u, 0x00u); /* set watchdog error counter */

(void)Sbc_Spi_Write(0x1Du, 0x80u); /* lin control */

(void)Sbc_Spi_Write(0x29u, 0x20u); /* reset pluse width = 15ms */

(void)Sbc_Spi_Write(0x1Cu, 0xE8u); /* set SWE */

(void)Sbc_Spi_Write(0x18u, 0x00u); /* clear FSM counter */

(void)Sbc_Spi_Read(0x18u); /* set FSM state */

(void)Sbc_Spi_Write(0x17u, 0x30u); /* set reset method and enable FSM */