Part Number: TL16C750E

Other Parts Discussed in Thread: TL16C750

こんにちは。

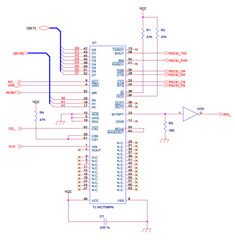

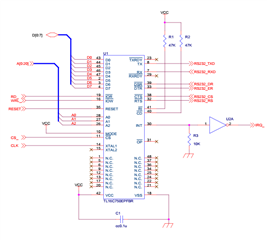

製品改訂に伴い、製品のUARTをTL16C750からTL16C750Eへの変更を検討しています。

添付図のようにUARTと回路を変更したところ、起動時からSRAMへの書き込みができず、端末が暴走状態になってしまいました。 しかし、TL16C750回路はそうではありませんでした。

基板からUARTを取り外したところ、正常に動作したので、UART周辺の回路に問題があると思いました。

デバイス起動時にUARTチップセットがディスエーブルされると、データバス端子はハイインピーダンスになりますが、実際にはデータバスは出力状態になっていました。

その後、チップセットを有効にしてデバイスをリセットすると、データバスがハイインピーダンスになりました。

データシートを確認しましたが、チップセットを有効にしてリセットするという記載はありませんでした。

以下の点について教えてください。

・TL16C750とTL16C750Eの相性(端末機能の違いなど)

・起動時やリセット時の挙動についてですが、この挙動は正しいですか?

ありがとうございます。