Part Number: DS90UB928Q-Q1

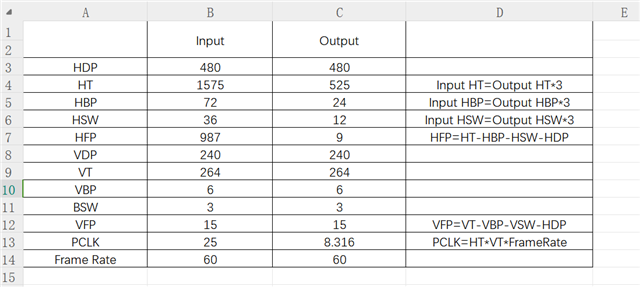

The minimum clock frequency of ds90ub928 output pattern is 25M, but the clock range of our screen is 7.32~10.433M. Now we want to complete the time sequence conversion through the distortion correction chip S2D13V40, but the output image is not on the screen, please help to check whether the configuration of ds90ub928 is correct.

Input and output timing of S2D13V40:

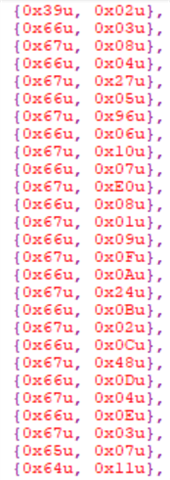

the configuration of ds90ub928