HI ti:

The timing set by SOC side is as follows(1 clk lane+4 data lane):

h_active=1920, hbp=32, hfp=48, hsw=48, v_hactive=720, vbp=4, vfp=4, vsw=8

pixel clk=91Mhz, dsi rate=600Mbps/lane

The des is 948, We tried to measure the timing of the 948 output, but but it didn't match what we set in soc.

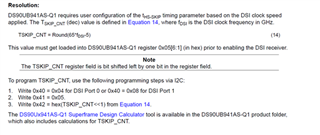

Refer to <941 bring up guide.pdf>, which gives the conversion between DSI clock frequency and video PCLK according to the following formula: f_PCLK = (f_DSI*N_Lanes)/12, f_PCLK = (300*4)/12=100Mhz calculated by this formula is inconsistent with 91M set at the SOC.

How does 941 parse the DSI data sent by SOC? How is clock, VFP, VBP, HFP, HBP time sequence reconstructed?