Other Parts Discussed in Thread: PCA9306

Hi, TI Colleagues

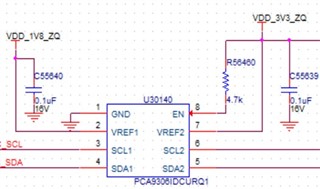

Our one product use the PCA9306 and VREF2 directly connect to VDD_3V3,detail as bleow shows. Currently it pass the DV and PV test. We're wondering if there is some potential risk for this and what's the risk?

If the FET in chip was damaged because of the large current, what's the failure mode, VREF1 disconnect with VREF2? or VREF1 and VREF2 short together?