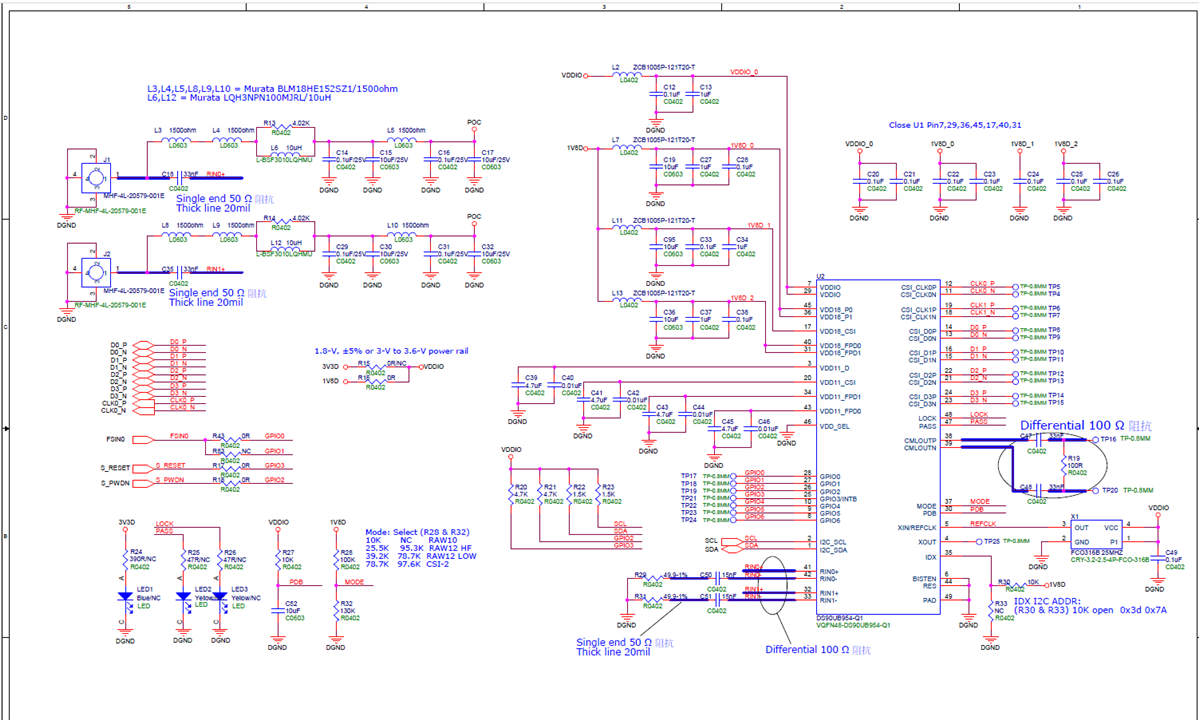

Part Number: DS90UB954-Q1

Tool/software:

Dear Sir,

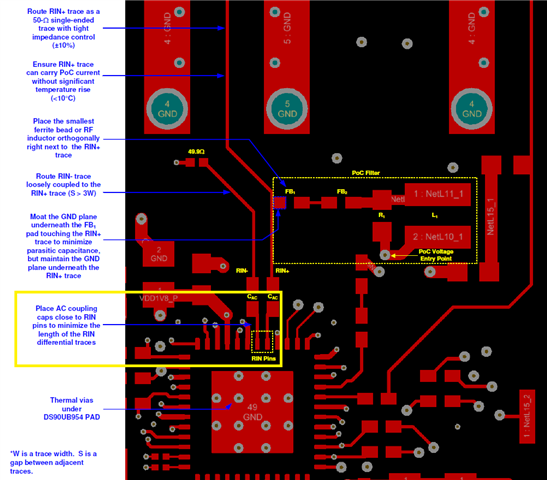

We try sync mode on 953/954 and we can get the image send by sensor(cable is 10m).

We are transmitting 2560*720@30fps video data, and the Mipi datarate is 1.6Gbps/lane.

Cable:STP

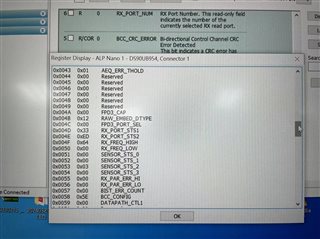

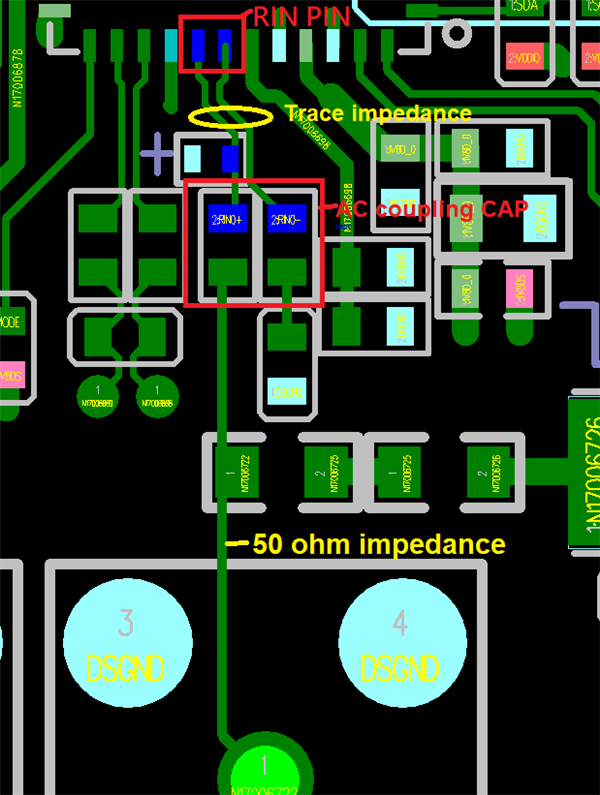

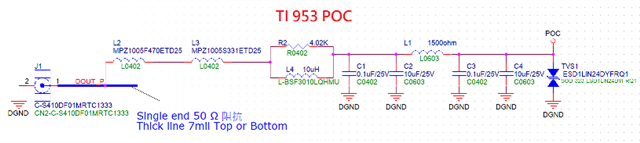

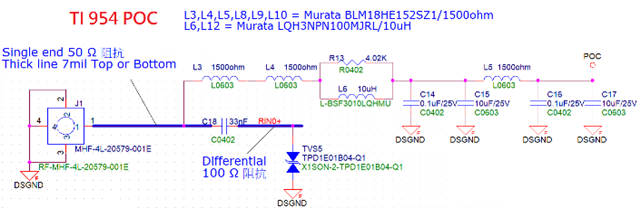

The images we received are as follows,Sometimes it is normal, but sometimes the video often fail is as follows picture1 & 2.

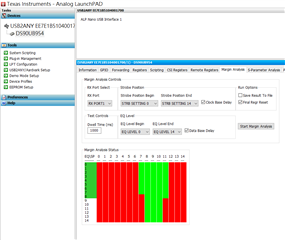

We try running the margin analysis program,the result is as follows picture3.

Can you give some suggestions for improvement?