Tool/software:

Hello,

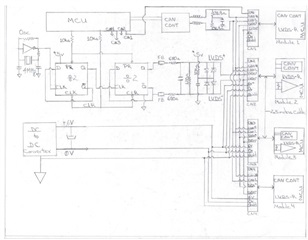

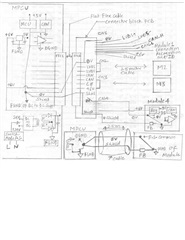

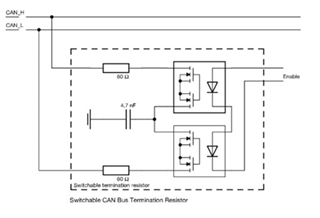

We have a system where LVDS Driver output signal has Vcm = 2.1V with Vid = 1.1V (each LVDS line swings from 2.1V to 2.65V with respect to ground when connected to a single 120 ohm input terminated LVDS receiver through 2.5 meter cable) at 1 MHz that is used as reference clock. It means the Vcm exceeds the (2.4V - Vid/2) LVDS input requirement for the standard LVDS receivers. Can we use DS91M125 to distribute this non standard LVDS signal (reference clock) to 4 different modules, using 2.5 meter cable (Zo = 120 Ohm, shielded twisted pair) to connect each module to DS91M125 and standard LVDS receiver with 120 ohm termination at its input? The existing configuration has this LVDS driver output connected in parallel to 4 separate modules, each module has 2.5 meter cable that feeds a LVDS receiver with 120 Ohm termination resistor. We suspect that the parallel connection of 4 LVDS receivers through cable to a single driver, is not a stable design though the original designer seem to have incorporated the LVDS driver with higher output to drive the effective load of 30 Ohms. Is there a chip with single M-LVDS receiver available, preferably in SOT23 package?

What would happen if one of the driver's outputs (either inverting or non-inverting or both) of DS91M125, are left open circuit while the corresponding Enable (DE) pin is active high? Would it cause any issues/noise with other three driver outputs that are enabled and properly terminated?

Thank you.