Part Number: DP83867E

Tool/software:

Hi, Expert

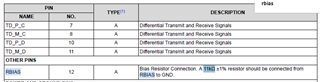

Data sheet recommend RBIAS resistor value should be 11kΩ. I think this value works fine (11kΩ) on customized board, but got failed for ethernet compliance test.

Customer try to reduce RBIAS resistor to 8kΩ, and then ethernet compliance test pass.

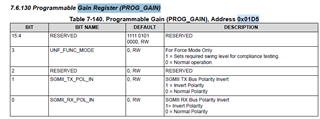

we also try to adjust Gain Register (PROG_GAIN), Reg 0x1D5 = 0xF508 with RBIAS resistor 11kΩ, and it also gets fail for ethernet compliance test. (Sets required swing level for compliance testing)

My question.

(1) What's resistor value range for RBIAS?

(2) Do it have any side effect to reduce RBIAS resistor value? because I am not sure it is a normal workaround way.

(3) What's mean to reduce RBIAS resistor? Does it have any defect on customer's board design?

I already reference this thread.

I feel confuse, because most of user case try to modify RBIAS resistor to 10kΩ is sufficient

Many Thanks

Gibbs