Other Parts Discussed in Thread: TDA2

Tool/software:

Hi PHY team,

May you have a good day! My customer meet with a question, please help to give a reply:

Hardware Background: They use SOC: TDA2S +PHY Chip: DP83TC813S;

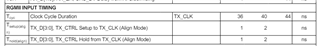

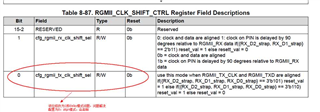

Software configuration: SOC side RGMII interface (RX and TX are configured for align mode), PHY: DP83TC813S (RX is delay mode, TX is configured for align mode);

Problem: Frames are dropped when the computer is connected to the light transfer.

Workaround: Resolve by modifying the 602 register bit 0 = 1 on the PHY side, as follows:

They have two questions:

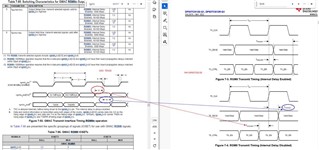

Question 1: Please help to provide the timing diagram of the SOC-side (TDA2S) align mode, which can be matched with the phy-side (delay) mode;

Question 2: The SOC side defaults to delay mode in the manual, which is based on whether the SOC is delay mode, the PHY must be align mode. Timing is as below:

Best Regards,

Jack