Other Parts Discussed in Thread: THVD1406

Tool/software:

Dear Expert

There is a phenomenon of error code failure in our communication here.

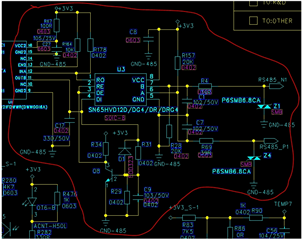

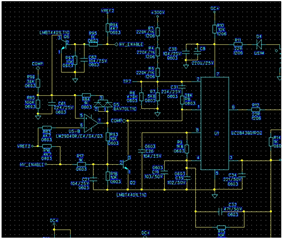

Test signal quality and rise/fall slope. The signal quality from U3 front to isolated IC to chip end is very good (the level voltage and rise/fall slope meet the requirements, less than 2us, impeccable), which means that the signal quality at the output end of U3 backend deteriorates;

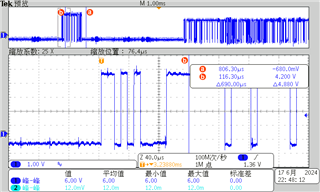

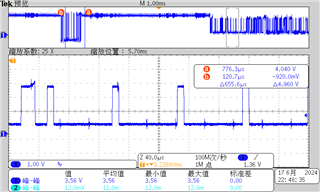

The signal quality of RS485_11 is as follows: waveform, falling edge, and slope.

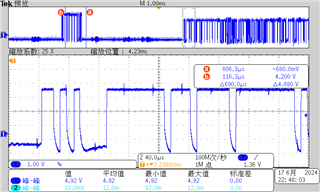

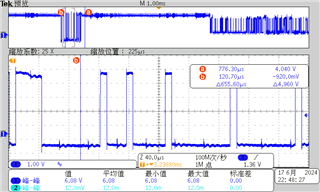

The signal quality of RS485-P1 is good, with the following waveform:

The voltage changes at the two signal terminals are unstable, and the RS485_11 signal has a downward slope, resulting in poor signal quality. Attempted to adjust parameters to optimize but did not see any improvement. Suspect if it is due to chip or USB communication issues? Or it may be due to the coordination of the RS485 communication box, which is currently unclear.