Tool/software:

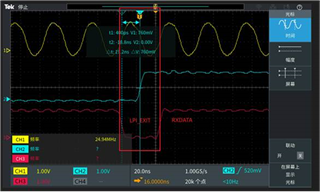

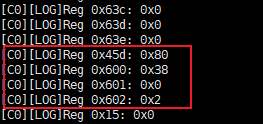

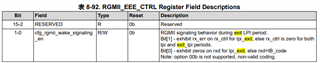

I am using DP83TC812S-Q1 to communicate with MAC which doesn't support eee. It seems that the lpi_exit signal (as descriped in RGMII_EEE_CTRL Register 0x603) is sent every time data is received. Rx_ER on rx_ctrl is assertted but the MAC cannot recognized it. The configuration of this register cannot take effect. Here are my questions:

1. Will the lpi exit signal be sent every time data is received from idle status under the default configuration?

2. Can I stop the eee feature of DP83TC812S-Q1 in rgmii mode and stop the lpi exit signal by software configuration?