Part Number: DP83867CR

Tool/software:

Hi Team,

Customer's use of TI DP83867CR PHY,

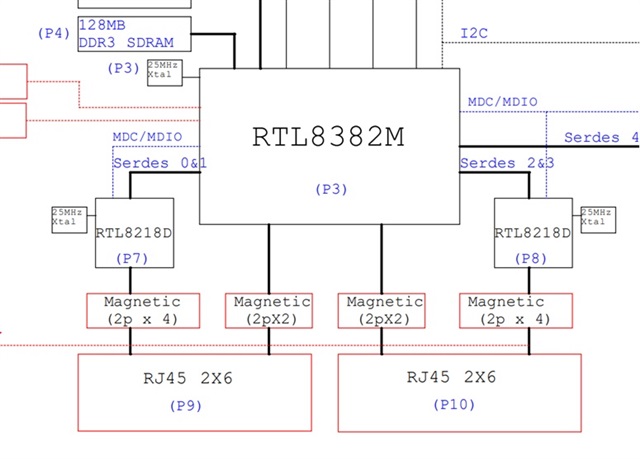

The architecture connected to the PoE switch is as follows:

MAC uses RTL8382M (integrated 8port 1G PHY)

Two external RTL8218D (8 port 1G PHY)

Customers found that there are two different situations when using the TI DP83867CR port to connect to the switch.

1. Connect to the port of RTL8382M, it can work normally and transmit at the highest speed without any problem.

2. Connect to the port of RTL8218D, the transmission rate is only 30-40%.

Does DP83867CR have compatibility issues with RTL8218D?

Can DP83867CR set or improve this compatibility issues?