Part Number: DP83867IR

Tool/software:

Hi TI Experts:

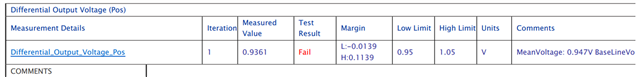

We have a 100base-T Ethernet SI test base on TI DP83867IR. And the “Differential output voltage Pos” is fail.

Because the mechanical limitation we have to route a long trace for the ethernet signal.

After read the document 《DP83867 Troubleshooting Guide》, I find some suggestion for the compliance test from TI doc“DP83867 Troubleshooting Guide”.

It said could adjust the register to improve the test.

After change the value of the register 0x00A0 from 0x606 to 0x609 the Ethernet compliant test was pass.

Q1:

But after read the Linux device driver of dp83867.c [https://github.com/TexasInstruments/ti-ethernet-software/blob/main/linux_drivers/dp83867.c], I found this driver does not support setting register 0xA0. Can I add the function of configuring register 0xA0 in the driver? If so, when should I set this value, after phy reset and before phy restart or after other step?

Q2:

From the DP83867IR datasheet, it was said that the default value of register 0x00A0 is set by trim, Can you tell me what trim means?

Q3:

Can we modify the I/O Configuration( Address 0x0170) to make the "Differential output voltage Pos" test pass?

Thanks

Best regards

Snow