Other Parts Discussed in Thread: , HD3SS3220

Tool/software:

Hi,

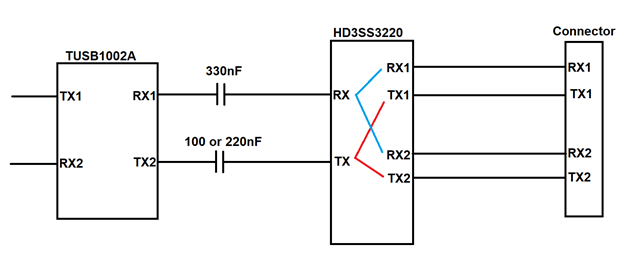

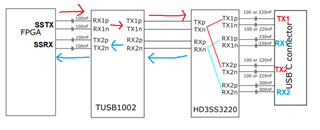

I am using the TUSB1002 and the HD3SS3220 in a SuperSpeedPlus (10Gbps) application which connects an FPGA via the TUSB1002 and HD3SS3220 to a USB C connector. The attached image shows the connections along with AC decoupling capacitors. Could you review the way I have connected this and let me know if I need to make any changes for correct operation. Also, if I use the TUSB1002A will the connections still be the same.

Thank you,

Liam