Part Number: DS100DF410

Other Parts Discussed in Thread: DS125DF1610, DS125DF111

Tool/software:

Hi,

Below is copied from the another post, are these the same input signal requirement for DS100DF410 CDR locking? Thank you!

Here are some possibilities for the ds125df1610 CDR not locking.

- Signal data-rate incompatible with retimer

- Invalid signal sub-rate is being used

- Valid signal sub-rate is being used (div2/4/8), but device DS125DF1610 register config is not set to the proper sub-rate

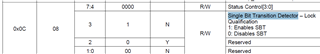

- Signal does not have a high enough density of bit transitions for CDR to lock ( channel register 0x0C[3] )

- Signal does not meet PPM check criteria ( channel register 0x2F[2] )

- Insertion loss at receiver end exceeds the maximum EQ of the retimer

Best,

Zach