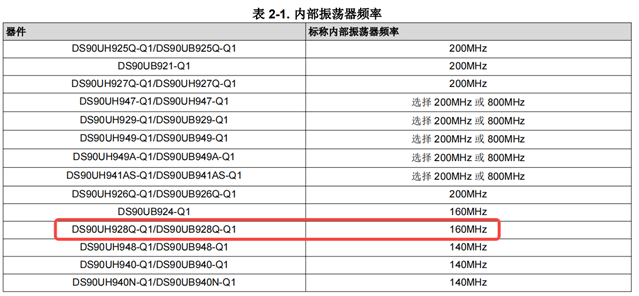

Part Number: DS90UB928Q-Q1

Tool/software:

Now we have a project that wants to output the pattern image with 928, but there is no image after configuring the relevant register of 928 through MCU. The display parameter we need is as follows:

![]()

The register list we configured for 928 via MCU is shown as below ,(according to SNLA132);

#define PGIA 0X66//!< 间接地址寄存器

#define PGID 0X67//!< 间接数据寄存器

(0X01,0X06);

(0X02,0XF0);

(0X1c,0X03);

(PGIA,0x03);

(PGID,0x05);

(PGIA,0x07);

(PGID,0x56);

(PGIA,0x08);

(PGID,0x03);

(PGIA,0x09);

(PGID,0x1E);

(PGIA,0x04);

(PGID,0xE8);

(PGIA,0x05);

(PGID,0xD3);

(PGIA,0x06);

(PGID,0x20);

(PGIA,0x0C);

(PGID,0x48);

(PGIA,0x0D);

(PGID,0x09);

(PGIA,0x0A);

(PGID,0x06);

(PGIA,0x0B);

(PGID,0x01);

(PGIA,0x0E);

(PGID,0x03);

(0x65,0x04);

(0x39,0x02);

(0x64,0x41);

I2C communication is normal , After configuration, the pattern is not displayed in practice, and the test PLCK is only more than 27MHz, and VS is only 53Hz.However, HFP, HBP and HSW, VSW waveforms are the same as the parameters we set, Please help to check whether there is any configuration we missed or any suggestions.