Tool/software:

Hello,

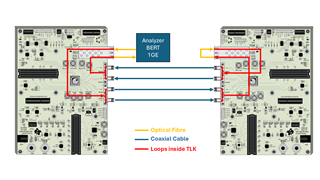

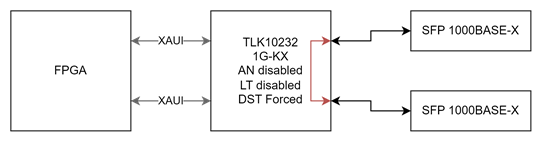

We are using TLK10232 in one of our designs, which can be summarized with the next diagrams:

Mode of operation 1 (10GBASE-R):

We managed to make this mode work by finding the most suitable equalization parameters for our system, after following the bringup procedures.

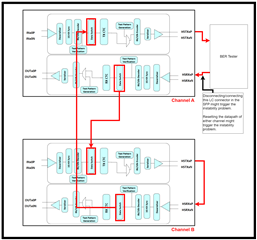

Mode of operation 2 (1000BASE-X):

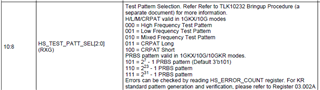

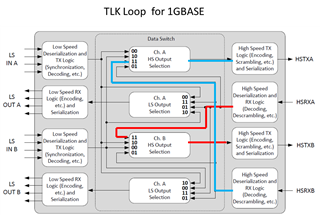

In this mode we don't need to pass through the FPGA, so we thought that the fastest way to achieve 1000BASE-X regeneration was to enable the DST switch setting the reserved bits 30.23.4:0 (DST_FORCE_SEL) to 0b11000. This sets the dataswitch configuration like the next image:

The LS side would be unused, although the FPGA might be driving the LS lanes (IN) with XAUI data.

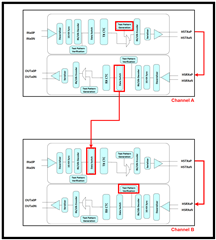

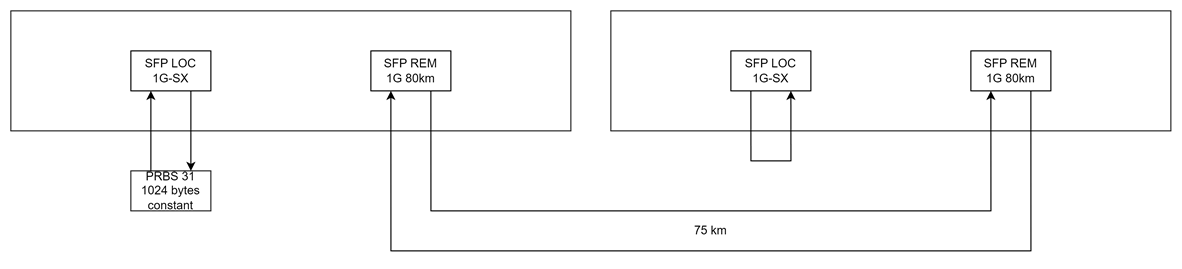

We are struggling to make this mode work reliably. We can leave a test (see image below) for 60+ hours with no issues, but if we disconnect/connect the LC connectors in any of the SFP modules several times, the system ends up not being able to leave KX_RX_FAULT state and the communication is broken.

We have monitored HS_CHANNEL_STATUS_1 (30.15) register and we see the next values:

HS_DECODE_INVALID 1

HS_CHANNEL_SYNC 0

KX_RX_FAULT 1

Most of the time we solve the problem by issuing a datapath reset, but it isn't guaranteed to work always.

Any idea on what could be causing the issue?