Other Parts Discussed in Thread: USB2ANY

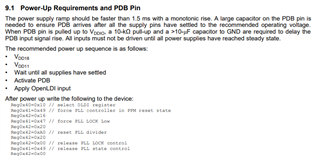

Tool/software:

Hi TI,

case1:947设置Single link & Dual-pixel mode,打lvds信号给948,948出现异常,无法识别和读写;

case2:947设置Single link & Single-pixel mode,打lvds信号给948,948是正常的,但是无显示;

-------------------------------------------------------------------------------------------

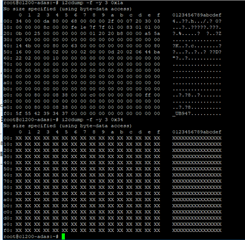

case1,打lvds信号后,dump 947&948 寄存器信息如下:

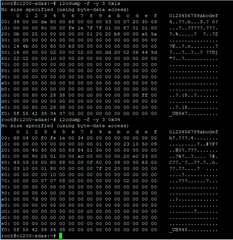

case2,打lvds信号后,dump 947&948 寄存器信息如下:

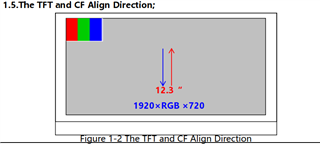

按照屏的需求,应该是要设置成 Dual-pixel mode,请问该如何设置?

Thanks.