Other Parts Discussed in Thread: DS90UB948-Q1

Tool/software:

HI expert,

Several questions need you help to confirm about 941.

1) If use the Dual FPD-Link III mode, does it need use the 2x 4Lane MIPI DSI input? DSI0 and DSI1.

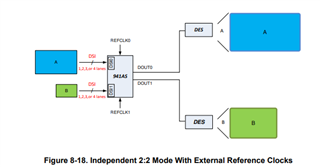

2) When is the external reference clock REFCLK used? Is it recommended to use an internal or external reference clock? What should I be aware of if I don't use the external reference clock REFCLK? For REFCLK0 whether it corresponds to DSI0? For REFCLK1, whether it corresponds to DSI1?

3) How to choose Clock Modes? For 4lane's MIPI CSI, Dual FPD-Link III mode, what modes are recommended for MODE_SEL0, MODE_SEL1 in the Table8-9 and Table8-10? The display deserializer is DS90UB948-Q1 and uses dual Open LDI mode.

4)What are the two models of SPLITTER Mode and DISABLE DSI?

Thanks a lot!

Andy