Tool/software:

Hello Team,

The setup is quite simple, UB947 > UB948. Could you please give some advice how to solve this problem?

I could generate internal pattern via the following configurations attached. I know the UB948 is locked to UB947 by checking DSUB948_ReadBytes(0x28) and DSUB948_ReadBytes(0x1C)

Thanks

Kexiang

the setup could generate internal pattern via the following configurations:

// initialize the page 10 after power up

DSUB947_WriteBytes(0x40,0x10); // select OLDI register

DSUB947_WriteBytes(0x41,0x49); // force PLL controller in PPM reset state

DSUB947_WriteBytes(0x42,0x16);

DSUB947_WriteBytes(0x41,0x47); // force PLL LOCK Low

DSUB947_WriteBytes(0x42,0x20);

DSUB947_WriteBytes(0x42,0xA0); // reset PLL divider

DSUB947_WriteBytes(0x42,0x20);

DSUB947_WriteBytes(0x42,0x00); // release PLL LOCK control

DSUB947_WriteBytes(0x41,0x49);

DSUB947_WriteBytes(0x42,0x00); // release PLL state control

// 2C Control

DSUB947_WriteBytes( 0x03, 0xDA);

DSUB947_WriteBytes( 0x17, 0x9E);

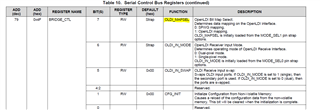

// BRIDGE_CTL

DSUB947_WriteBytes(0x4F, 0xC0); // Single-pixel mode, OpenLDI mapping

// Gate RGB data with DE

DSUB947_WriteBytes(0x04,0x90); //Prevent AVMUTE for non-HDCP systems

//DUAL_CTL1

DSUB947_WriteBytes(0x5B,0x03); //Force dual FPD-Link, enable reset on PLL frequency change

//BCC Watchdog Control

DSUB947_WriteBytes(0x16,0x02); //Adjust BCC watchdog timer to minimum

//GPIO Pass through

DSUB947_WriteBytes(0x0E,0x35);

DSUB947_WriteBytes(0x0F,0x03);

DSUB948_WriteBytes(0x1E,0x53);

DSUB948_WriteBytes(0x1F,0x05);

// Initialize UB948

DSUB948_WriteBytes(0x4A,0x01); //Disable OLDI outputs on 948 to prevent screen glitches from appearing during the init process

DSUB948_WriteBytes(0x01,0x01); // snapshot reset

//Sleep 100ms

//Initialize SPI Mode

DSUB947_WriteBytes(0x43,0x06);

DSUB948_WriteBytes(0x43,0x06);

DSUB948_WriteBytes(0x4A,0x00); // Enable OLDI outputs on UB948

DSUB948_WriteBytes( 0x26, 0x16);

DSUB948_WriteBytes( 0x27, 0x16);

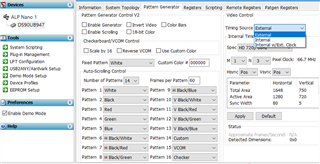

//PATGEN programming

DSUB947_WriteBytes(0x64, 0x10); //disabled patttern

DSUB947_WriteBytes(0x66, 0x04);

DSUB947_WriteBytes(0x67, 0x91);

DSUB947_WriteBytes(0x66, 0x05);

DSUB947_WriteBytes(0x67, 0x05); // h Total = 1425

DSUB947_WriteBytes(0x66, 0x06);

DSUB947_WriteBytes(0x67, 0x31); // v Total = 784

DSUB947_WriteBytes(0x66, 0x07);

DSUB947_WriteBytes(0x67, 0x00);

DSUB947_WriteBytes(0x66, 0x08);

DSUB947_WriteBytes(0x67, 0x05); //h Active = 1280

DSUB947_WriteBytes(0x66, 0x09);

DSUB947_WriteBytes(0x67, 0x30); //v Active = 768

DSUB947_WriteBytes(0x66, 0x0a);

DSUB947_WriteBytes(0x67, 0x28); // h sw = 40

DSUB947_WriteBytes(0x66, 0x0b);

DSUB947_WriteBytes(0x67, 0x02); //v sw = 2

DSUB947_WriteBytes(0x66, 0x0c);

DSUB947_WriteBytes(0x67, 0x32); //h bp = 50

DSUB947_WriteBytes(0x66, 0x0d);

DSUB947_WriteBytes(0x67, 0x06); //v bp = 6

DSUB947_WriteBytes(0x66, 0x1a);

DSUB947_WriteBytes(0x67, 0x09); //M=9

DSUB947_WriteBytes(0x66, 0x03);

DSUB947_WriteBytes(0x67, 0x61); //N=97 > 74.22

DSUB947_WriteBytes(0x65, 0x04); //internal clock and timing

DSUB947_WriteBytes(0x64, 0x05); // enable colorbar

// Force dual-link mode

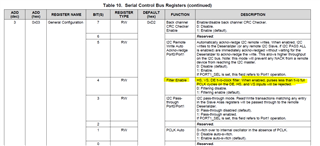

DSUB948_WriteBytes(0x34,0x0A); // PORT1_SEL

DSUB948_WriteBytes(0x28,0x10);

// Forward SPI channel after RX is locked to TX by checking DSUB948_ReadBytes(I2C_ADDR_DSUB948, 0x1c)

DSUB947_WriteBytes(0x1E, 0x02);

DSUB947_WriteBytes(0x0F, 0x03);

DSUB947_WriteBytes(0x0E, 0x35);

DSUB947_WriteBytes(0x0D, 0x03);

DSUB948_WriteBytes(0x34,0x0A); // PORT1_SEL

DSUB948_WriteBytes(0x4B,0x02); // Adjust 0x4B

DSUB948_WriteBytes(0x1F,0x02); // GPIO3

DSUB948_WriteBytes(0x1E,0x02); // GPIO2-GPIO1 SPCLK MISO

DSUB948_WriteBytes(0x1D,0x02); // GPIO0 MOSI

DSUB948_WriteBytes( 0x43, 0x06); // Forward SPI channel

//////////////////////////////////////////////////////////////////////////////////////////////

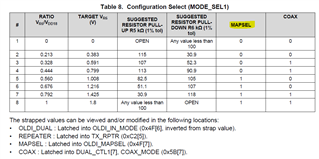

DSUB948 is loss of lock once changed into external timing mode via the step:

DSUB947_Write(0x65, 0x0C);

//DSUB947_Write(0x65, 0x00); // default external timing enabled