Part Number: DS90UB928Q-Q1

Tool/software:

Hi,

Our customer has a question about SCL.

1.

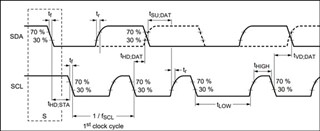

Is the definition of SCL High/Low Time (relationship to SCL frequency) correct as follows?

SCL Freq = Rise Time(tr) + SCL High Time(tHigh) + Fall Time(tf) + SCL Low Time(tLow)

In a previous post, I learned that SCL has a maximum 20% variation.

2.

Does the maximum 20% deviation between the register setting value and the measured value change depending on the surrounding environment?

For example, if the deviation is 5% when the IC is shipped, will it become 10% or 3% during operation?

Or is the deviation always constant?

3. Is the above deviation due to individual differences? Or is it variation between lots?

Best regards,

Hiroshi