Other Parts Discussed in Thread: TFP401

Tool/software:

Dear, Support Team.

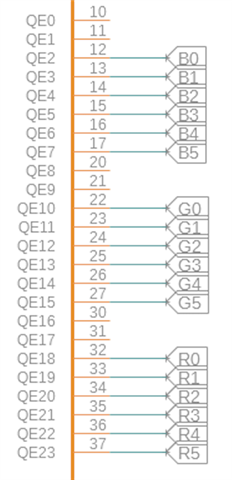

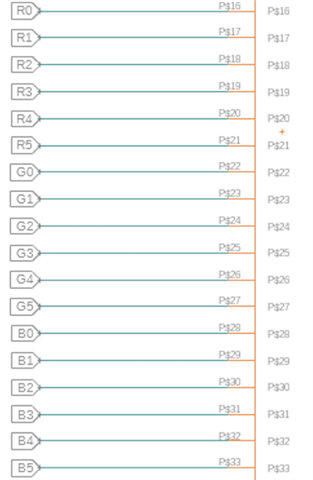

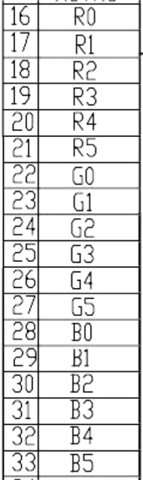

We are currently using the TFP401APZP chip for a 480x480 resolution, 18-bit color depth display.

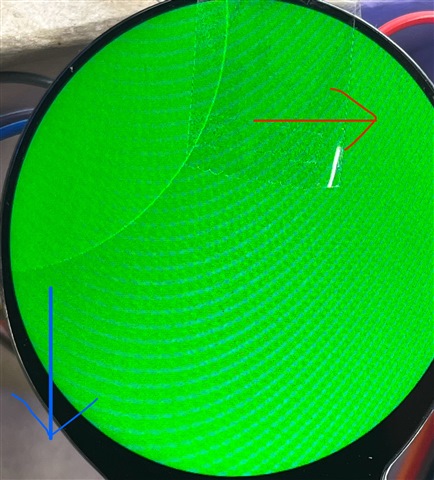

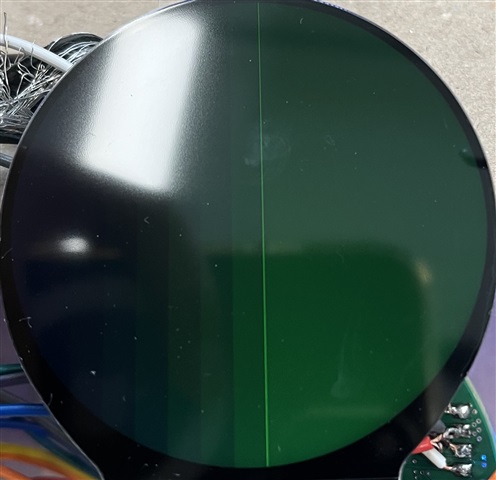

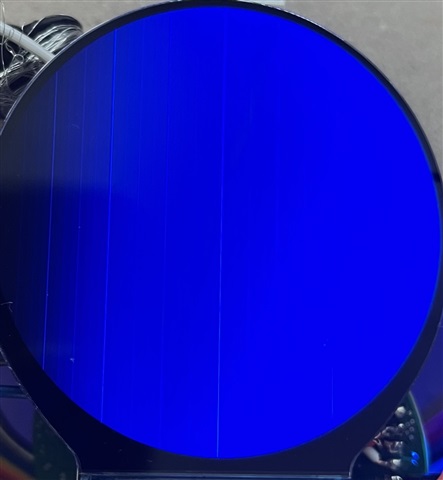

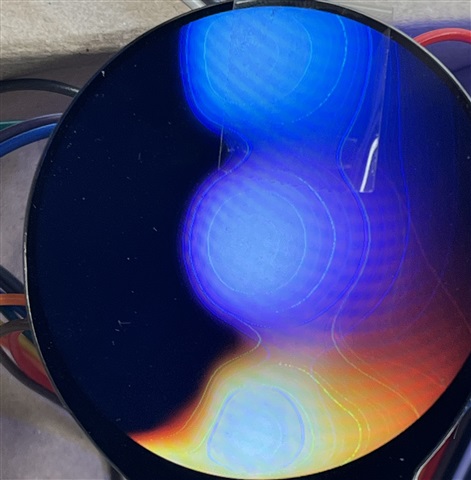

We are encountering an unusual issue where a distinct line appears along the horizontal boundaries of color values.

This line disappears along the vertical axis.

Notably, this is not a case of color banding.

The below shader is used to generate a green gradient image above, where the minimum color width is expected to be 32 pixels.

However, the issue presents with a 1-pixel line that appears contrary to this expectation.

// GLSL

void main()

{

vec2 coord = gl_FragCoord.xy;

ivec3 ic = ivec3(0, int(coord.x) / 32, 0);

if (ic.y > 7)

{

ic.y = 8;

}

fragColor = vec4(vec3(ic) / 255.0, 1.0);

}Configuration:

Raspberry Pi 4 HDMI -> TFP401 -> (Drop 2LSB) -> Display driver(ST7701SN)

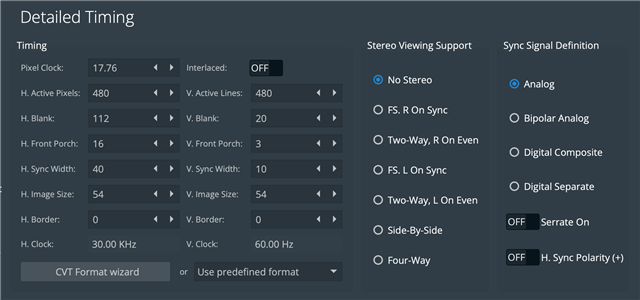

Below is Display Timing info used for HDMI.

The display works correctly when directly interfaced with an ESP32 using an 18-bit RGB configuration.

We have reviewed our hardware setup and found no apparent issues

We welcome any advice or suggestions you might have.

Best regards,

Gunwoo Ahn