Other Parts Discussed in Thread: TCA39306

FAQ: Logic and Voltage Translation > IxC >> What is PassFET Hangtime?

To understand what passFET hangtime is, we need to define what a passFET is.

A passFET is a transistor where the drain and source terminals are interchangeable. The drain can be the source and the source can be the drain depending on the direction of communication.

This is especially import in I2C applications where bi-directional communication must occur for the protocol to work.

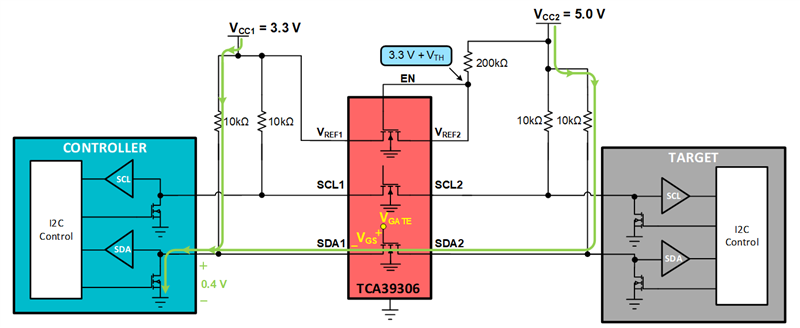

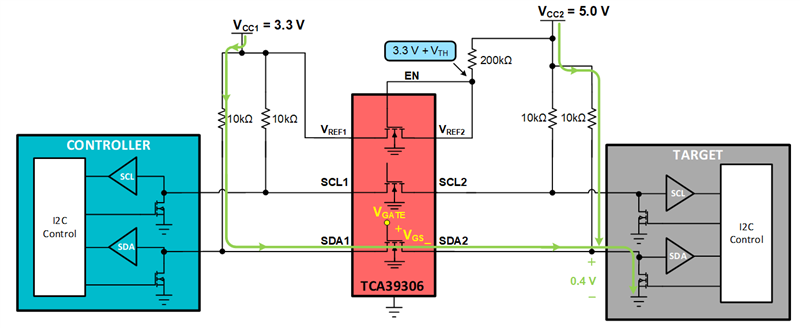

An example of a device that uses a passFET is the TCA39306 I3C/I2C capable level translator.

Controller pulling LOW through the TCA39306 level translator.

Target pulling LOW through the TCA39306 level translator.

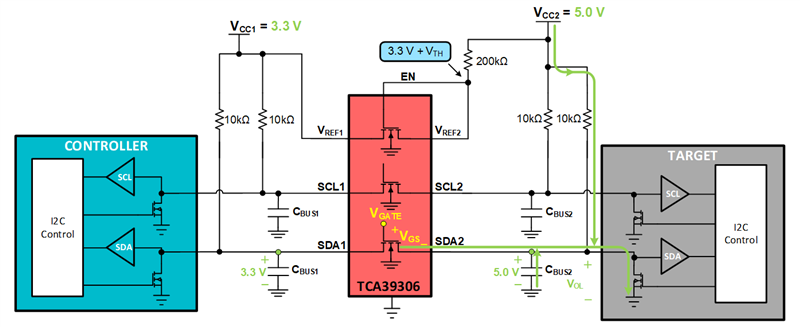

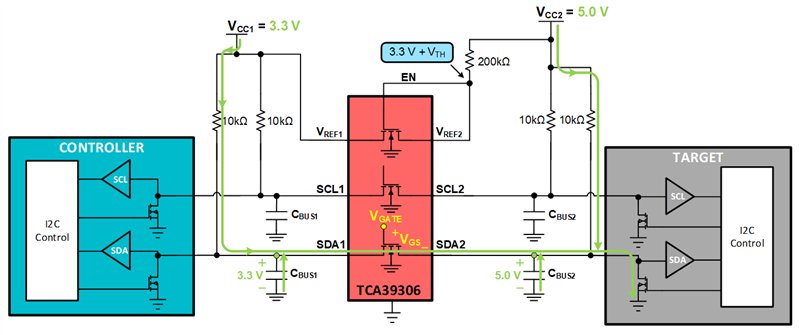

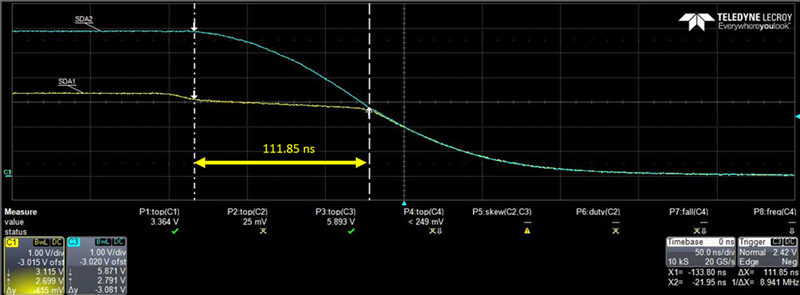

PassFET hangtime is the time that the bus "hangs" during a high to low transition. PassFET hangtime occurs due to the parasitic capacitance on the I2C bus (CBUS1 & CBUS2). In the example below, the target pulls the bus LOW. It must first discharge the parasitic capacitance CBUS2 pulling the source of the passFET towards GND. Once the threshold voltage of the passFET between SDA1 and SDA2 has been surpassed the target sees the excess charge on CBUS1 in which the bus hangs.

Target pulls LOW.

Target pulls LOW and begins to see the charge on CBUS1 in which the bus hangs for a time.

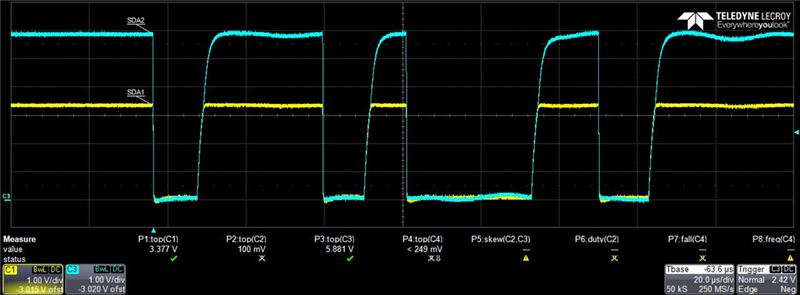

Below is an I2C address being sent.

CH1 = YELLOW = SDA1

CH2 = BLUE = SDA2

The effect of hang time is unnoticeable until the time scale is changed.

PassFET hangtime is measured to 111.85 ns in this example. Not enough time to make a significant impact on an I2C system, but the transition is there.

For more information on passFET hangtime, please see this application note.