Tool/software:

Hi

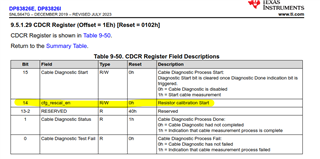

I randomly experiment link issue in linux and after some investigation, I discovered when the problem happen, the bit 14 in the CDCR register (cfg_rescal_en) is set after the releasing of the reset. Writing 0 to shit bit makes the link come up. Does anybody knows something about this bit ? There is no information in the datasheet or related documentation to this part and this bit is not present in other family part datasheet... For now, the workaround to fix the problem is clearing this bit after the reset in the linux driver, but I do not know if doing that has side effect...