Tool/software:

In our A sample board, after we reset phy and then read register 0x45d, the value is 0xd1a0, but in B sample board,the value is 0xffff.

A sample:

B sample:

Our soc is SA8295, the register log is

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

Tool/software:

In our A sample board, after we reset phy and then read register 0x45d, the value is 0xd1a0, but in B sample board,the value is 0xffff.

A sample:

B sample:

Our soc is SA8295, the register log is

the partial log is:

Jan 01 00:00:08.592 devnp_emac_eth0.45080 emac0 26 [emac_mdio_dump_phy_registers:2153]: ************* PHY Reg dump *************************

Jan 01 00:00:08.594 devnp_emac_eth0.45080 emac0 26 [emac_mdio_dump_phy_registers:2156]: Phy Control Reg(Basic Mode Control Reg) (0) = 0x140

Jan 01 00:00:08.596 devnp_emac_eth0.45080 emac0 26 [emac_mdio_dump_phy_registers:2161]: Phy Status Reg(Basic Mode Status Reg) (0x1) = 0x141

Jan 01 00:00:08.598 devnp_emac_eth0.45080 emac0 26 [emac_mdio_dump_phy_registers:2166]: Phy Id (PHYS ID 1) (0x2)= 0x2000

Jan 01 00:00:08.600 devnp_emac_eth0.45080 emac0 26 [emac_mdio_dump_phy_registers:2171]: Phy Id (PHYS ID 2) (0x3)= 0xa284

Jan 01 00:00:08.602 devnp_emac_eth0.45080 emac0 26 [emac_mdio_dump_phy_registers:2176]: Auto-nego Adv (Advertisement Control Reg) (0x4) = 0

Jan 01 00:00:08.604 devnp_emac_eth0.45080 emac0 26 [emac_mdio_dump_phy_registers:2182]: Auto-nego Lap (Link Partner Ability Reg) (0x5)= 0

Jan 01 00:00:08.606 devnp_emac_eth0.45080 emac0 26 [emac_mdio_dump_phy_registers:2187]: Auto-nego Exp (Extension Reg)(0x6) = 0

Jan 01 00:00:08.608 devnp_emac_eth0.45080 emac0 26 [emac_mdio_dump_phy_registers:2192]: Auto-nego Exp (Extension Reg)(0x7) = 0

Jan 01 00:00:08.610 devnp_emac_eth0.45080 emac0 26 [emac_mdio_dump_phy_registers:2196]: Auto-nego Np (0x8) = 0

Jan 01 00:00:08.612 devnp_emac_eth0.45080 emac0 26 [emac_mdio_dump_phy_registers:2201]: 1000 Ctl Reg (1000BASE-T Control Reg)(0x9) = 0

Jan 01 00:00:08.614 devnp_emac_eth0.45080 emac0 26 [emac_mdio_dump_phy_registers:2205]: 1000 Sts Reg (1000BASE-T Status)(0xa) = 0

Jan 01 00:00:08.616 devnp_emac_eth0.45080 emac0 26 [emac_mdio_dump_phy_registers:2209]: MDI Register (0xb) = 0

Jan 01 00:00:08.618 devnp_emac_eth0.45080 emac0 26 [emac_mdio_dump_phy_registers:2213]: MDI Register (0xc) = 0

Jan 01 00:00:08.620 devnp_emac_eth0.45080 emac0 26 [emac_mdio_dump_phy_registers:2217]: MDI Register (0xd) = 0

Jan 01 00:00:08.622 devnp_emac_eth0.45080 emac0 26 [emac_mdio_dump_phy_registers:2221]: MDI Register (0xe) = 0

Jan 01 00:00:08.624 devnp_emac_eth0.45080 emac0 26 [emac_mdio_dump_phy_registers:2225]: Extended Status Reg (0xf) = 0

Jan 01 00:00:08.626 devnp_emac_eth0.45080 emac0 26 [emac_mdio_dump_phy_registers:2229]: Vendor Base Reg (0x10) = 0x4

Jan 01 00:00:08.628 devnp_emac_eth0.45080 emac0 26 [emac_mdio_dump_phy_registers:2234]: PHY Sts Reg (0x11) = 0xb

Jan 01 00:00:08.630 devnp_emac_eth0.45080 emac0 26 [emac_mdio_dump_phy_registers:2238]: MDI Register (0x12) = 0

Jan 01 00:00:08.632 devnp_emac_eth0.45080 emac0 26 [emac_mdio_dump_phy_registers:2242]: MDI Register (0x13) = 0

Jan 01 00:00:08.634 devnp_emac_eth0.45080 emac0 26 [emac_mdio_dump_phy_registers:2246]: MDI Register (0x14) = 0

Jan 01 00:00:08.636 devnp_emac_eth0.45080 emac0 26 [emac_mdio_dump_phy_registers:2250]: MDI Register (0x15) = 0

Jan 01 00:00:08.638 devnp_emac_eth0.45080 emac0 26 [emac_mdio_dump_phy_registers:2254]: MDI Register (0x16) = 0x100

Jan 01 00:00:08.640 devnp_emac_eth0.45080 emac0 26 [emac_mdio_dump_phy_registers:2258]: MDI Register (0x17) = 0

Jan 01 00:00:08.642 devnp_emac_eth0.45080 emac0 26 [emac_mdio_dump_phy_registers:2262]: MDI Register (0x18) = 0x8

Jan 01 00:00:08.644 devnp_emac_eth0.45080 emac0 26 [emac_mdio_dump_phy_registers:2266]: MDI Register (0x19) = 0x8

Jan 01 00:00:08.646 devnp_emac_eth0.45080 emac0 26 [emac_mdio_dump_phy_registers:2270]: MDI Register (0x1a) = 0

Jan 01 00:00:08.648 devnp_emac_eth0.45080 emac0 26 [emac_mdio_dump_phy_registers:2274]: MDI Register (0x1b) = 0

Jan 01 00:00:08.650 devnp_emac_eth0.45080 emac0 26 [emac_mdio_dump_phy_registers:2278]: MDI Register (0x1c) = 0

Jan 01 00:00:08.652 devnp_emac_eth0.45080 emac0 26 [emac_mdio_dump_phy_registers:2282]: MDI Register (0x1d) = 0

Jan 01 00:00:08.655 devnp_emac_eth0.45080 emac0 26 [emac_mdio_dump_phy_registers:2286]: MDI Register (0x1e) = 0

Jan 01 00:00:08.657 devnp_emac_eth0.45080 emac0 26 [emac_mdio_dump_phy_registers:2290]: MDI Register (0x1f) = 0

Hi Hui,

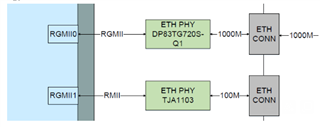

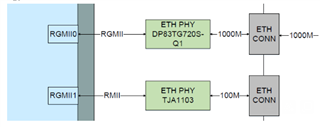

I don't see any differences in the A sample and B sample boards from your block diagram. Is there any difference in the hardware or software?

Can you confirm you are using the Linux driver provided here? https://github.com/TexasInstruments/ti-ethernet-software/tree/main

If not, please use the one provided at the link.

Issues with register access can be caused by multiple HW or SW issues. If the new driver does not work, we can try to confirm the HW is working by

(1) Measuring CLK_OUT on scope

(2) Measuring INH on multimeter

(3) Checking power up sequence

Best regards,

Melissa

Hi Melissa,

The driver runs on the qnx system, and the dp83tg720 driver code is the same, i have uploaded the driver code and block diagram of A sample and B sample.

please help me check it, thanks.

A sample:

B sample:

The driver code:

#include <sys/siginfo.h>

#include <quiesce.h>

#include <fcntl.h>

#include <string.h>

#include <netdrvr/mdi.h>

#include <nw_thread.h>

#include <amss/fdt_utils.h>

#include <amss/libfdt.h>

#include <sys/sockio.h>

#include "phy_wrapper.h"

#include "emac_globals.h"

#include "emac.h"

#define DP83TG720CS_1_1_PHY_ID 0x2000a284

#define DP83720_DEVADDR 0x1f

#define DP83720_DEVADDR_MMD1 0x1

#define MII_DP83720_INT_STAT1 0x12

#define MII_DP83720_INT_STAT2 0x13

#define MII_DP83720_INT_STAT3 0x18

#define MII_DP83720_RESET_CTRL 0x1f

#define DP83720_HW_RESET BIT(15)

#define DP83720_SW_RESET BIT(14)

#define DP83720_STRAP 0x45d

#define DP83720_SGMII_CTRL 0x608

#define SGMII_CONFIG_VAL 0x027B

/* INT_STAT1 bits */

#define DP83720_ANEG_COMPLETE_INT_EN BIT(2)

#define DP83720_ESD_EVENT_INT_EN BIT(3)

#define DP83720_LINK_STAT_INT_EN BIT(5)

#define DP83720_ENERGY_DET_INT_EN BIT(6)

#define DP83720_LINK_QUAL_INT_EN BIT(7)

/* INT_STAT2 bits */

#define DP83720_SLEEP_MODE_INT_EN BIT(2)

#define DP83720_OVERTEMP_INT_EN BIT(3)

#define DP83720_OVERVOLTAGE_INT_EN BIT(6)

#define DP83720_UNDERVOLTAGE_INT_EN BIT(7)

/* INT_STAT3 bits */

#define DP83720_LPS_INT_EN BIT(0)

#define DP83720_WAKE_REQ_EN BIT(1)

#define DP83720_NO_FRAME_INT_EN BIT(2)

#define DP83720_POR_DONE_INT_EN BIT(3)

/* SGMII CTRL bits */

#define DP83720_SGMII_AUTO_NEG_EN BIT(0)

#define DP83720_SGMII_EN BIT(9)

/* Strap bits */

#define DP83720_MASTER_MODE BIT(5)

#define DP83720_RGMII_IS_EN BIT(12)

#define DP83720_SGMII_IS_EN BIT(13)

#define DP83720_RX_SHIFT_EN BIT(14)

#define DP83720_TX_SHIFT_EN BIT(15)

/* RGMII ID CTRL */

#define DP83720_RGMII_ID_CTRL 0x602

#define DP83720_RX_CLK_SHIFT BIT(1)

#define DP83720_TX_CLK_SHIFT BIT(0)

#define ARRAY_SIZE(arr) (sizeof(arr) / sizeof((arr)[0]))

struct dp83720_init_reg {

int reg;

int val;

};

static const struct dp83720_init_reg dp83720_cs1_1_master_init[] = {

{0x405, 0x5800},

{0x8ad, 0x3c51},

{0x894, 0x5df7},

{0x8a0, 0x9e7},

{0x8c0, 0x4000},

{0x814, 0x4800},

{0x80d, 0x2ebf},

{0x8c1, 0xb00},

{0x87d, 0x001},

{0x82e, 0x000},

{0x837, 0x0f4},

{0x8be, 0x200},

{0x8c5, 0x4000},

{0x8c7, 0x2000},

{0x8b3, 0x05a},

{0x8b4, 0x05a},

{0x8b0, 0x202},

{0x8b5, 0x0ea},

{0x8ba, 0x2828},

{0x8bb, 0x6828},

{0x8bc, 0x028},

{0x8bf, 0x000},

{0x8b1, 0x014},

{0x8b2, 0x008},

{0x8ec, 0x000},

{0x8c8, 0x003},

{0x8be, 0x201},

{0x18c, 0x001},

};

void phy_write_c45(struct emac_prv_data_t *pdata, uint16_t devaddr, uint16_t offset, uint16_t phydata)

{

emac_mdio_write(pdata,pdata->phy_addr,0xd,devaddr);

emac_mdio_write(pdata,pdata->phy_addr,0xe,offset);

emac_mdio_write(pdata,pdata->phy_addr,0xd,0x4000 | devaddr);

emac_mdio_write(pdata,pdata->phy_addr,0xe,phydata);

printf("%s [%d].[0x%x].[0x%x] \n", __FUNCTION__, devaddr, offset, phydata);

}

int phy_read_c45(struct emac_prv_data_t *pdata, uint16_t devaddr, uint16_t offset)

{

emac_mdio_write(pdata,pdata->phy_addr,0xd,devaddr);

emac_mdio_write(pdata,pdata->phy_addr,0xe,offset);

emac_mdio_write(pdata,pdata->phy_addr,0xd,0x4000 | devaddr);

int data = emac_mdio_read(pdata,pdata->phy_addr,0xe);

if(data == -1){

return -1;

}

printf("%s [%d].[0x%x].[0x%x] \n", __FUNCTION__, devaddr, offset, data);

return data;

}

int dp83720_read_straps(struct emac_prv_data_t *pdata)

{

int strap;

strap = phy_read_c45(pdata, DP83720_DEVADDR, DP83720_STRAP);

if (strap < 0)

return strap;

if (strap & DP83720_MASTER_MODE)

printf("straps dp83720->is_master = true\n");

if (strap & DP83720_RGMII_IS_EN)

printf("straps dp83720->is_rgmii = true\n");

if (strap & DP83720_SGMII_IS_EN)

printf("straps dp83720->is_sgmii = true\n");

if (strap & DP83720_RX_SHIFT_EN)

printf("straps dp83720->rx_shift = true\n");

if (strap & DP83720_TX_SHIFT_EN)

printf("straps dp83720->tx_shift = true\n");

return 0;

};

void dp83720_reset(struct emac_prv_data_t *pdata, bool hw_reset)

{

if (hw_reset)

phy_write_c45(pdata, DP83720_DEVADDR, MII_DP83720_RESET_CTRL, DP83720_HW_RESET);

else

phy_write_c45(pdata, DP83720_DEVADDR, MII_DP83720_RESET_CTRL, DP83720_SW_RESET);

usleep(100); //65us

}

void dp83720_write_seq(struct emac_prv_data_t *pdata, const struct dp83720_init_reg *init_data, int size)

{

int i;

for (i = 0; i < size; i++) {

phy_write_c45(pdata, DP83720_DEVADDR, init_data[i].reg, init_data[i].val);

}

}

void dp83720_chip_init(struct emac_prv_data_t *pdata)

{

// hard reset

dp83720_reset(pdata, true);

// to configure phy in master mode

phy_write_c45(pdata, DP83720_DEVADDR_MMD1, 0x0834, 0xc001);

// to not let the phy start the link-up procedure

phy_write_c45(pdata, DP83720_DEVADDR, 0x573, 0x101);

// DSP settings for margins during OA EMC level-4 immunity test

dp83720_write_seq(pdata, dp83720_cs1_1_master_init, ARRAY_SIZE(dp83720_cs1_1_master_init));

// no rx tx delay

phy_write_c45(pdata, DP83720_DEVADDR, DP83720_RGMII_ID_CTRL, 0x0);

// soft reset

dp83720_reset(pdata, false);

// to let phy start the link-up procedure

phy_write_c45(pdata, DP83720_DEVADDR, 0x573, 0x001);

// to start the send-s detection during link-up sequence

phy_write_c45(pdata, DP83720_DEVADDR, 0x56a, 0x5f41);

}

void phy_switch_reset0(){

int ret = EOK;

int fd = open("/dev/gpio/soc_ephy0_rst/value", O_RDWR);

if (fd < 0) {

printf("[switch]%s: open soc_ephy0_rst errors \n", __func__);

ret = EINVAL;

}else {

printf("[switch]%s: open soc_ephy0_rst success!! \n", __func__);

write(fd, "0", sizeof("0"));

usleep(100000);

write(fd,"1",sizeof("1")); //set to high

usleep(200000);

if( 0 != lseek(fd, 0, SEEK_SET)) // Read the pin value back and log it

{

printf("%s: Error setting seek \n", __func__);

ret = EINVAL;

} else {

char buf;

memset(&buf,'0', sizeof(buf));

read(fd, &buf, sizeof(buf));

printf("[switch]PHY pin high = %c \n", buf);

}

if(close(fd) < 0) {

printf("%s: closing fd failed with %s \n", __func__,strerror(errno));

ret = EINVAL;

}

}

if (ret == EINVAL) {

printf("%s: PHY reset encountered errors \n", __func__);

}

}

void phy_switch_reset1(void){

int ret = EOK;

int fd = open("/dev/gpio/soc_ephy1_rst/value", O_RDWR);

if (fd < 0) {

printf("[switch]%s: open soc_ephy1_rst errors \n", __func__);

ret = EINVAL;

}else {

printf("[switch]%s: open soc_ephy1_rst success!! \n", __func__);

write(fd, "0", sizeof("0"));

usleep(100000);

write(fd,"1",sizeof("1")); //set to high

usleep(200000);

if( 0 != lseek(fd, 0, SEEK_SET)) // Read the pin value back and log it

{

printf("%s: Error setting seek \n", __func__);

ret = EINVAL;

} else {

char buf;

memset(&buf,'0', sizeof(buf));

read(fd, &buf, sizeof(buf));

printf("[switch]PHY pin high = %c \n", buf);

}

if(close(fd) < 0) {

printf("%s: closing fd failed with %s \n", __func__,strerror(errno));

ret = EINVAL;

}

}

if (ret == EINVAL) {

printf("%s: PHY reset encountered errors \n", __func__);

}

}

void dp83tg720_init(struct emac_prv_data_t *pdata)

{

int value;

phy_switch_reset0();

dp83720_read_straps(pdata);

dp83720_chip_init(pdata);

value = phy_read_c45(pdata, DP83720_DEVADDR_MMD1, 0x0834);

if (value & BIT(14))

printf("dp83720 current master\n");

value = phy_read_c45(pdata, DP83720_DEVADDR, 0x600);

if (value & BIT(3))

printf("dp83720 current rgmii\n");

value = phy_read_c45(pdata, DP83720_DEVADDR, 0);

if (value & BIT(6))

printf("dp83720 current 1000.00 Mb/s\n");

if (value & BIT(8))

printf("dp83720 current full-duplex\n");

value = phy_read_c45(pdata, DP83720_DEVADDR, 1);

if (value & BIT(2))

printf("dp83720 current link up\n");

else

printf("dp83720 current link down\n");

}

unsigned short dp83tg720_getSQI(struct emac_prv_data_t *pdata) {

static unsigned short first_time = 1;

static unsigned short prevSQI = 0;

unsigned short regValue;

unsigned short reg_link;

unsigned short mse_lock;

unsigned short result = 0x0;

reg_link = phy_read_c45(pdata, DP83720_DEVADDR, 0x0180);

regValue = phy_read_c45(pdata, DP83720_DEVADDR, 0x875);

mse_lock = (regValue & 0x3FF);

//comparison without hysterisis

if ((first_time == 1) && ((reg_link & 0x3007) == 0x3007)){

if (mse_lock >= 0x65) //threshold1_down

result = 0x1;

else if (mse_lock >= 0x50) //threshold2_down

result = 0x2;

else if (mse_lock >= 0x33) //threshold3_down

result = 0x3;

else

result = 0x4;

first_time = 0;

}else if ((first_time == 0) && ((reg_link & 0x3007) == 0x3007)){ ////comparison with hysterisis

if (prevSQI == 0x1){

if (mse_lock < 0x65) //threshold1_down

result = 0x2;

else

result = 0x1;

}else if (prevSQI == 0x2){

if (mse_lock < 0x50) //threshold2_down

result = 0x3;

else if (mse_lock > 0x72) //threshold2_up

result = 0x1;

else

result = 0x2;

}else if (prevSQI == 0x3){

if (mse_lock < 0x33) //threshold3_down

result = 0x4;

else if (mse_lock > 0x5E) //threshold3_up

result = 0x2;

else

result = 0x3;

}else if (prevSQI == 0x4){

if (mse_lock > 0x42) //threshold4_up

result = 0x3;

else

result = 0x4;

}

}else{ //sqi at link-loss

first_time = 1;

result = 0x0;

}

prevSQI = result;

return result;

}

Hi Melissa,

I added some logs in dp83tg720 driver, that is, after write a register, we read the value of the register. the log shows that the value of register is always 0xffff.

Jan 01 00:00:08.188 devnp_emac_eth0.45081 emac0 26 [phy_switch_reset0:219]: phy_switch_reset0: hhhhhhh

Jan 01 00:00:08.188 devnp_emac_eth0.45081 emac0 26 [phy_switch_reset0:229]: [switch]PHY pin high = 1

Jan 01 00:00:08.196 devnp_emac_eth0.45081 emac0 26 [phy_read_c45:126]: phy_read_c45 [31].[0x45d].[0xffff]

Jan 01 00:00:08.196 devnp_emac_eth0.45081 emac0 26 [dp83720_read_straps:138]: straps dp83720->is_master = true

Jan 01 00:00:08.196 devnp_emac_eth0.45081 emac0 26 [dp83720_read_straps:141]: straps dp83720->is_rgmii = true

Jan 01 00:00:08.196 devnp_emac_eth0.45081 emac0 26 [dp83720_read_straps:144]: straps dp83720->is_sgmii = true

Jan 01 00:00:08.196 devnp_emac_eth0.45081 emac0 26 [dp83720_read_straps:147]: straps dp83720->rx_shift = true

Jan 01 00:00:08.196 devnp_emac_eth0.45081 emac0 26 [dp83720_read_straps:150]: straps dp83720->tx_shift = true

Jan 01 00:00:08.204 devnp_emac_eth0.45081 emac0 26 [phy_write_c45:113]: phy_write_c45 [31].[0x1f].[0x8000]

Jan 01 00:00:08.214 devnp_emac_eth0.45081 emac0 26 [phy_write_c45:113]: phy_write_c45 [31].[0x573].[0x101]

Jan 01 00:00:08.222 devnp_emac_eth0.45081 emac0 26 [phy_read_c45:126]: phy_read_c45 [31].[0x573].[0xffff]

Jan 01 00:00:08.230 devnp_emac_eth0.45081 emac0 26 [phy_write_c45:113]: phy_write_c45 [1].[0x834].[0xc001]

Jan 01 00:00:08.238 devnp_emac_eth0.45081 emac0 26 [phy_read_c45:126]: phy_read_c45 [1].[0x834].[0xffff]

Jan 01 00:00:08.247 devnp_emac_eth0.45081 emac0 26 [phy_write_c45:113]: phy_write_c45 [31].[0x405].[0x5800]

Jan 01 00:00:08.256 devnp_emac_eth0.45081 emac0 26 [phy_read_c45:126]: phy_read_c45 [31].[0x405].[0xffff]

Jan 01 00:00:08.266 devnp_emac_eth0.45081 emac0 26 [phy_write_c45:113]: phy_write_c45 [31].[0x8ad].[0x3c51]

Jan 01 00:00:08.275 devnp_emac_eth0.45081 emac0 26 [phy_read_c45:126]: phy_read_c45 [31].[0x8ad].[0xffff]

Jan 01 00:00:08.284 devnp_emac_eth0.45081 emac0 26 [phy_write_c45:113]: phy_write_c45 [31].[0x894].[0x5df7]

Jan 01 00:00:08.295 devnp_emac_eth0.45081 emac0 26 [phy_read_c45:126]: phy_read_c45 [31].[0x894].[0xffff]

Jan 01 00:00:08.306 devnp_emac_eth0.45081 emac0 26 [phy_write_c45:113]: phy_write_c45 [31].[0x8a0].[0x9e7]

Jan 01 00:00:08.316 devnp_emac_eth0.45081 emac0 26 [phy_read_c45:126]: phy_read_c45 [31].[0x8a0].[0xffff]

Jan 01 00:00:08.327 devnp_emac_eth0.45081 emac0 26 [phy_write_c45:113]: phy_write_c45 [31].[0x8c0].[0x4000]

Jan 01 00:00:08.336 devnp_emac_eth0.45081 emac0 26 [phy_read_c45:126]: phy_read_c45 [31].[0x8c0].[0xffff]

Jan 01 00:00:08.347 devnp_emac_eth0.45081 emac0 26 [phy_write_c45:113]: phy_write_c45 [31].[0x814].[0x4800]

Jan 01 00:00:08.358 devnp_emac_eth0.45081 emac0 26 [phy_read_c45:126]: phy_read_c45 [31].[0x814].[0xffff]

Jan 01 00:00:08.368 devnp_emac_eth0.45081 emac0 26 [phy_write_c45:113]: phy_write_c45 [31].[0x80d].[0x2ebf]

Jan 01 00:00:08.377 devnp_emac_eth0.45081 emac0 26 [phy_read_c45:126]: phy_read_c45 [31].[0x80d].[0xffff]

Jan 01 00:00:08.387 devnp_emac_eth0.45081 emac0 26 [phy_write_c45:113]: phy_write_c45 [31].[0x8c1].[0xb00]

Jan 01 00:00:08.396 devnp_emac_eth0.45081 emac0 26 [phy_read_c45:126]: phy_read_c45 [31].[0x8c1].[0xffff]

Jan 01 00:00:08.407 devnp_emac_eth0.45081 emac0 26 [phy_write_c45:113]: phy_write_c45 [31].[0x87d].[0x1]

Jan 01 00:00:08.416 devnp_emac_eth0.45081 emac0 26 [phy_read_c45:126]: phy_read_c45 [31].[0x87d].[0xffff]

Jan 01 00:00:08.427 devnp_emac_eth0.45081 emac0 26 [phy_write_c45:113]: phy_write_c45 [31].[0x82e].[0x0]

Jan 01 00:00:08.436 devnp_emac_eth0.45081 emac0 26 [phy_read_c45:126]: phy_read_c45 [31].[0x82e].[0xffff]

Jan 01 00:00:08.445 devnp_emac_eth0.45081 emac0 26 [phy_write_c45:113]: phy_write_c45 [31].[0x837].[0xf4]

Jan 01 00:00:08.456 devnp_emac_eth0.45081 emac0 26 [phy_read_c45:126]: phy_read_c45 [31].[0x837].[0xffff]

Jan 01 00:00:08.468 devnp_emac_eth0.45081 emac0 26 [phy_write_c45:113]: phy_write_c45 [31].[0x8be].[0x200]

Jan 01 00:00:08.478 devnp_emac_eth0.45081 emac0 26 [phy_read_c45:126]: phy_read_c45 [31].[0x8be].[0xffff]

Jan 01 00:00:08.488 devnp_emac_eth0.45081 emac0 26 [phy_write_c45:113]: phy_write_c45 [31].[0x8c5].[0x4000]

Jan 01 00:00:08.499 devnp_emac_eth0.45081 emac0 26 [phy_read_c45:126]: phy_read_c45 [31].[0x8c5].[0xffff]

Jan 01 00:00:08.507 devnp_emac_eth0.45081 emac0 26 [phy_write_c45:113]: phy_write_c45 [31].[0x8c7].[0x2000]

Jan 01 00:00:08.515 devnp_emac_eth0.45081 emac0 26 [phy_read_c45:126]: phy_read_c45 [31].[0x8c7].[0xffff]

Jan 01 00:00:08.524 devnp_emac_eth0.45081 emac0 26 [phy_write_c45:113]: phy_write_c45 [31].[0x8b3].[0x5a]

Jan 01 00:00:08.535 devnp_emac_eth0.45081 emac0 26 [phy_read_c45:126]: phy_read_c45 [31].[0x8b3].[0xffff]

Jan 01 00:00:08.546 devnp_emac_eth0.45081 emac0 26 [phy_write_c45:113]: phy_write_c45 [31].[0x8b4].[0x5a]

Jan 01 00:00:08.556 devnp_emac_eth0.45081 emac0 26 [phy_read_c45:126]: phy_read_c45 [31].[0x8b4].[0xffff]

Jan 01 00:00:08.567 devnp_emac_eth0.45081 emac0 26 [phy_write_c45:113]: phy_write_c45 [31].[0x8b0].[0x202]

Jan 01 00:00:08.578 devnp_emac_eth0.45081 emac0 26 [phy_read_c45:126]: phy_read_c45 [31].[0x8b0].[0xffff]

Jan 01 00:00:08.588 devnp_emac_eth0.45081 emac0 26 [phy_write_c45:113]: phy_write_c45 [31].[0x8b5].[0xea]

Jan 01 00:00:08.598 devnp_emac_eth0.45081 emac0 26 [phy_read_c45:126]: phy_read_c45 [31].[0x8b5].[0xffff]

Jan 01 00:00:08.608 devnp_emac_eth0.45081 emac0 26 [phy_write_c45:113]: phy_write_c45 [31].[0x8ba].[0x2828]

Jan 01 00:00:08.621 devnp_emac_eth0.45081 emac0 26 [phy_read_c45:126]: phy_read_c45 [31].[0x8ba].[0xffff]

Jan 01 00:00:08.631 devnp_emac_eth0.45081 emac0 26 [phy_write_c45:113]: phy_write_c45 [31].[0x8bb].[0x6828]

Jan 01 00:00:08.640 devnp_emac_eth0.45081 emac0 26 [phy_read_c45:126]: phy_read_c45 [31].[0x8bb].[0xffff]

Jan 01 00:00:08.651 devnp_emac_eth0.45081 emac0 26 [phy_write_c45:113]: phy_write_c45 [31].[0x8bc].[0x28]

Jan 01 00:00:08.659 devnp_emac_eth0.45081 emac0 26 [phy_read_c45:126]: phy_read_c45 [31].[0x8bc].[0xffff]

Jan 01 00:00:08.668 devnp_emac_eth0.45081 emac0 26 [phy_write_c45:113]: phy_write_c45 [31].[0x8bf].[0x0]

Jan 01 00:00:08.678 devnp_emac_eth0.45081 emac0 26 [phy_read_c45:126]: phy_read_c45 [31].[0x8bf].[0xffff]

Jan 01 00:00:08.687 devnp_emac_eth0.45081 emac0 26 [phy_write_c45:113]: phy_write_c45 [31].[0x8b1].[0x14]

Jan 01 00:00:08.698 devnp_emac_eth0.45081 emac0 26 [phy_read_c45:126]: phy_read_c45 [31].[0x8b1].[0xffff]

Jan 01 00:00:08.706 devnp_emac_eth0.45081 emac0 26 [phy_write_c45:113]: phy_write_c45 [31].[0x8b2].[0x8]

Jan 01 00:00:08.716 devnp_emac_eth0.45081 emac0 26 [phy_read_c45:126]: phy_read_c45 [31].[0x8b2].[0xffff]

Jan 01 00:00:08.726 devnp_emac_eth0.45081 emac0 26 [phy_write_c45:113]: phy_write_c45 [31].[0x8ec].[0x0]

Jan 01 00:00:08.736 devnp_emac_eth0.45081 emac0 26 [phy_read_c45:126]: phy_read_c45 [31].[0x8ec].[0xffff]

Jan 01 00:00:08.745 devnp_emac_eth0.45081 emac0 26 [phy_write_c45:113]: phy_write_c45 [31].[0x8c8].[0x3]

Jan 01 00:00:08.755 devnp_emac_eth0.45081 emac0 26 [phy_read_c45:126]: phy_read_c45 [31].[0x8c8].[0xffff]

Jan 01 00:00:08.765 devnp_emac_eth0.45081 emac0 26 [phy_write_c45:113]: phy_write_c45 [31].[0x8be].[0x201]

Jan 01 00:00:08.776 devnp_emac_eth0.45081 emac0 26 [phy_read_c45:126]: phy_read_c45 [31].[0x8be].[0xffff]

Jan 01 00:00:08.786 devnp_emac_eth0.45081 emac0 26 [phy_write_c45:113]: phy_write_c45 [31].[0x18c].[0x1]

Jan 01 00:00:08.795 devnp_emac_eth0.45081 emac0 26 [phy_read_c45:126]: phy_read_c45 [31].[0x18c].[0xffff]

Jan 01 00:00:08.804 devnp_emac_eth0.45081 emac0 26 [phy_write_c45:113]: phy_write_c45 [31].[0x602].[0x0]

Jan 01 00:00:08.814 devnp_emac_eth0.45081 emac0 26 [phy_read_c45:126]: phy_read_c45 [31].[0x602].[0xffff]

Jan 01 00:00:08.824 devnp_emac_eth0.45081 emac0 26 [phy_write_c45:113]: phy_write_c45 [31].[0x1f].[0x4000]

Jan 01 00:00:08.836 devnp_emac_eth0.45081 emac0 26 [phy_write_c45:113]: phy_write_c45 [31].[0x573].[0x1]

Jan 01 00:00:08.846 devnp_emac_eth0.45081 emac0 26 [phy_read_c45:126]: phy_read_c45 [31].[0x573].[0xffff]

Jan 01 00:00:08.855 devnp_emac_eth0.45081 emac0 26 [phy_write_c45:113]: phy_write_c45 [31].[0x56a].[0x5f41]

Jan 01 00:00:08.866 devnp_emac_eth0.45081 emac0 26 [phy_read_c45:126]: phy_read_c45 [31].[0x56a].[0xffff]

Jan 01 00:00:08.875 devnp_emac_eth0.45081 emac0 26 [phy_read_c45:126]: phy_read_c45 [1].[0x834].[0xffff]

Jan 01 00:00:08.875 devnp_emac_eth0.45081 emac0 26 [dp83tg720_init:286]: dp83720 current master

Jan 01 00:00:08.884 devnp_emac_eth0.45081 emac0 26 [phy_read_c45:126]: phy_read_c45 [31].[0x600].[0xffff]

Jan 01 00:00:08.884 devnp_emac_eth0.45081 emac0 26 [dp83tg720_init:290]: dp83720 current rgmii

Jan 01 00:00:08.894 devnp_emac_eth0.45081 emac0 26 [phy_read_c45:126]: phy_read_c45 [31].[0x0].[0xffff]

Jan 01 00:00:08.894 devnp_emac_eth0.45081 emac0 26 [dp83tg720_init:294]: dp83720 current 1000.00 Mb/s

Jan 01 00:00:08.894 devnp_emac_eth0.45081 emac0 26 [dp83tg720_init:297]: dp83720 current full-duplex

Jan 01 00:00:08.903 devnp_emac_eth0.45081 emac0 26 [phy_read_c45:126]: phy_read_c45 [31].[0x1].[0xffff]

Jan 01 00:00:08.903 devnp_emac_eth0.45081 emac0 26 [dp83tg720_init:301]: dp83720 current link up

Hi Hui,

Since you are using the same driver code between the two samples, it might be an issue with the HW. Thank you for providing these measurements. Could you circle the schematic differences between A sample or B sample? The text in the photo is hard to read.

Looking at your CLK_OUT signal, it looks like the scale is set to 50 miliseconds/square, so the frequency is around ~20 Hz, is this correct? The frequency should be 25 MHz.

Best regards,

Melissa

Hi Hui,

Thanks for updating. I will close this thread now.

Best regards,

Melissa