Other Parts Discussed in Thread: ONET1131EC

Tool/software:

Hi team,

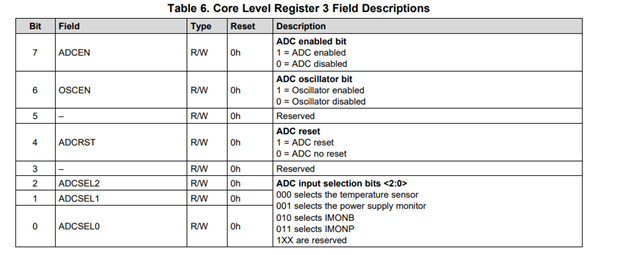

Below is the register of ONET1130EC and as you see there are different signal which can be sampled by ADC. If the customer use IMONB as ADC input signal firstly, then they want to switch to IMONP as ADC input signal. How long time does it take to finish IMONB signal sample for ONET1130EC, then to switch to signal IMONP?