Other Parts Discussed in Thread: ALP, USB2ANY

Tool/software:

We have appled the parameters as follows:

0x4C,0x01, //RX Port0 write enable

0x58,0x5E, //I2C pass-through, BCC 50Mbps

0x07,0xFF, // disable BCC watchdog

0x09,0x81,

0x5C,0xb0, //933 address

//0x5D,0x06, //camera address

//0x65,0xB2, //camera address

0x4C,0x12, //RX Port1 write enable

0x58,0x5E, //I2C pass-through, BCC 50Mbps

0x07,0xFF, // disable BCC watchdog

0x09,0x81,

0x5C,0xb0, //933 address

//0x5D,0x06, //camera address

//0x65,0xB2, //camera address

0x4C,0x24, //RX Port2 write enable

0x58,0x5E, //I2C pass-through, BCC 50Mbps

0x07,0xFF, // disable BCC watchdog

0x09,0x81,

0x5C,0xb0, //933 address

//0x5D,0x06, //camera address

//0x65,0xB2, //camera address

0x4C,0x38, //RX Port3 write enable

0x58,0x5E, //I2C pass-through, BCC 50Mbps

0x07,0xFF, // disable BCC watchdog

0x09,0x81,

0x5C,0xb0, //933 address

//0x5D,0x06, //camera address

//0x65,0xB2, //camera address

0x5E,0xDA, //GW5200 physical address

0x66,0xDA, //GW5200 alias address

0x5F,0xD8, //GW5200 failsafe address

0x67,0xD8, //GW5200 failsafe address

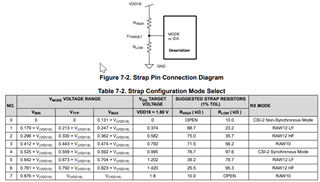

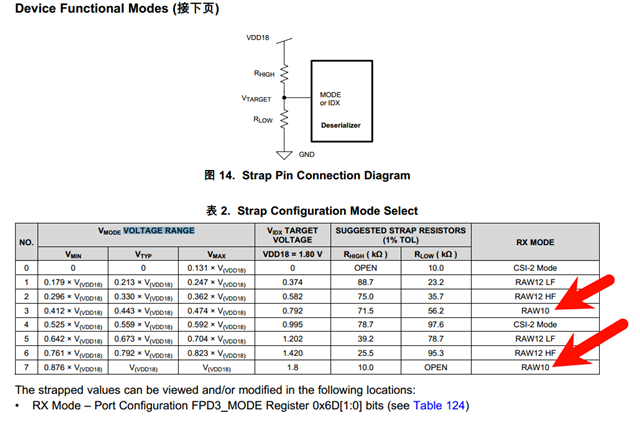

0x6D,0x7C, //CSI setting

0x6E,0xA8, //BC_GPIO0=0, GC_GPIO1=Fsync

0x70,0x1E, //vc0,YUV422

0x72,0xE4, //vc0

0x7C,0xC1,

0x32,0x01,

0x33,0x03,// #CSI OUT ENABLE ,enable continuous clock

0x20,0xC0,// #CSI FORWARDING PORT0,1

//frame sync settings, For 25-Mbps backchannel operation,

//the frame period is 1200 ns (30 bits x 40 ns/bit).

//30fps, 33333333/1200=27777=0x6C81

//0x6E,0xA0,

//0x19,0x0C,//FS_HIGH_TIME_1

//0x1A,0x81,//FS_HIGH_TIME_0

//0x1B,0x60,//FS_LOW_TIME_1

//0x1C,0x00,//FS_LOW_TIME_0

//0x18,0x01,//FrameSync Enable

//50fps

//frame sync settings, For 50-Mbps backchannel operation,

//the frame period is 600 ns (30 bits x 20 ns/bit).

//50fps, 20000000/600=33333=0x8235

0x6E,0xA0,

0x19,0x02,//FS_HIGH_TIME_1

0x1A,0x35,//FS_HIGH_TIME_0

0x1B,0x80,//FS_LOW_TIME_1

0x1C,0x00,//FS_LOW_TIME_0

0x18,0x01,//FrameSync Enable

then input a ntsc camera, but can not show the camera picture, and the MIPI has waveform.

The question is how we can check and investigate it?