Tool/software:

Hello:

Problem:EDP LCD power on timing issue (sleep wake-up jitter)

After continuous sleep and wake-up, it is easy to experience overall screen flickering and jumping, and the positioning and power on timing are not properly adjusted.

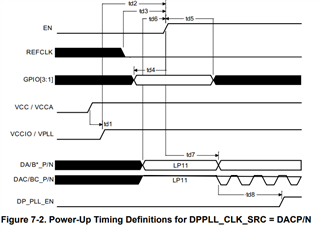

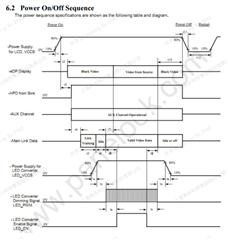

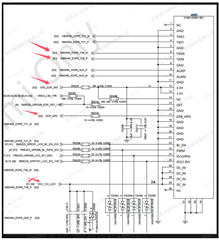

The complete screen power on/off timing diagram is as follows, requiring a certain time difference requirement to be met

Focus on the signals of the following pins

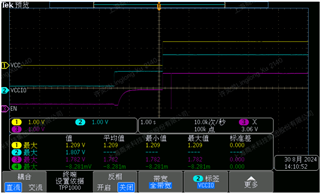

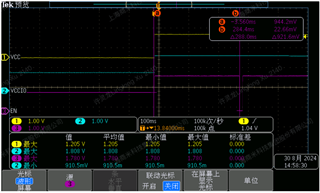

Power on timing

TXN0 and TXN1 power on first, 3V3 power on later, with an interval of 2.74ms

After 3V3 is powered on, HPD is powered on with an interval of 83.6ms

After HPD is powered on, TXN0 and TXN1 are powered on again with an interval of 361.4ms

Note: TXN0 and TXN1 have a first power on voltage of 0.308V and a second power on voltage of 0.468V

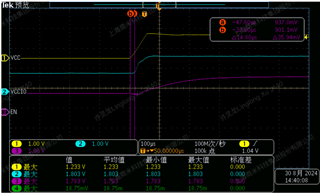

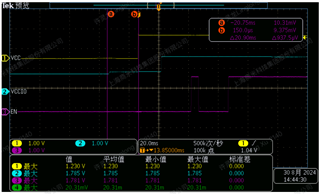

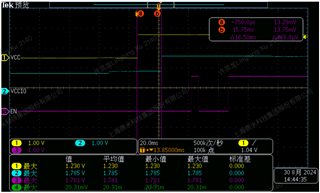

Wake up timing after hibernation

TXN0 and TXN1 power on first, 3V3 power on later, with an interval of 29.8ms, which is much higher than the startup interval of 2.74ms

After 3V3 is powered on, TXN0 and TXN1 are powered on again with an interval of 63.44ms

After TXNO is powered on twice, HPD is powered on last with an interval of 28.92ms

This is the waveform diagram of the wake-up signal from sleep mode

Based on the above test results,

1、there are some issues with TI's output. The EDP timing output by TI chips does not meet the timing requirements of the screen. Among them, TXN0 and TXN1 cannot be controlled by Android. Do you have some suggestion about this timing issue?

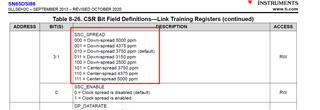

2、The customer would like to modify the frequency of the SN65DSI86 chip for verification and requires more explanation and clarification on the frequency expansion

What are the exhibition frequencies here? Percentage or something else