Part Number: DS90UB936-Q1

Tool/software:

Hi Team,

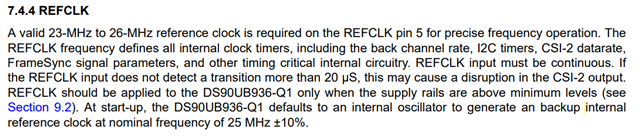

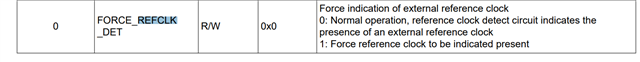

I would like to check if there is a scenario that our crystal can't output REFCLK to 936 well. Do we see the black screen or the 935/936 would switch to internal CLK to generate the PCLK?

Regards,

Roy