Other Parts Discussed in Thread: DS90UB953-Q1

Tool/software:

Hey FPD-Link team,

I have a customer using the DS90UB960-Q1 and the DS90UB953-Q1 on a project and we were hoping you could help to provide some guidance on two items. See below:

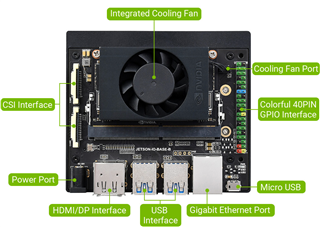

- We were having stability issues with capture on our setup that uses ub960 as deserializer and ub953 as serializers on a custom platform. We are trying to do some platform independent testing with an NVIDIA devkit instead of our custom hardware to try and pinpoint what is causing the huge number of CRC errors and constant channel unlocks that we are getting. Our idea is to ideally use the ub960 EVM, with the Xavier NX devkit, but said evm uses Mipi-60 as the csi-2 outputs. And the devkit uses ribbons as the csi-2 inputs, see image below. We wanted to check if there is any other evaluation kit or adapter that can meet our needs to have ribbons as the NVIDIA Xavier NX devkit uses. Is there an adapter or another evaluation kit that uses the UB960, that is compatible with NVIDIA's Jetson Xavier NX devkit?

- Regarding the forward channel's speed, we are using Synchronous mode and from our understanding, this mode uses a REFCLK that goes to the deserializer to provide via the back channel a clk for the serializer. We wanted to try and reduce/change the speed of it to see if the stability improves/changes. However, on our current platform and from looking at the datasheets we seem to be stuck with the speed that the refclk dictates, in our case 4Gbps with a 25MHz refclk. Is there a SW based way of using register configuration to change the forward channel's speed without altering the hw, i.e. keeping the current mode resistors or crystal osc?

Best regards,

Matt