Part Number: DS90UB941AS-Q1

Other Parts Discussed in Thread: ALP, USB2ANY

Tool/software:

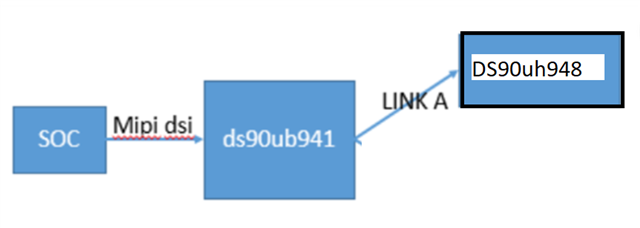

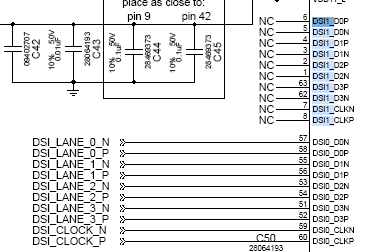

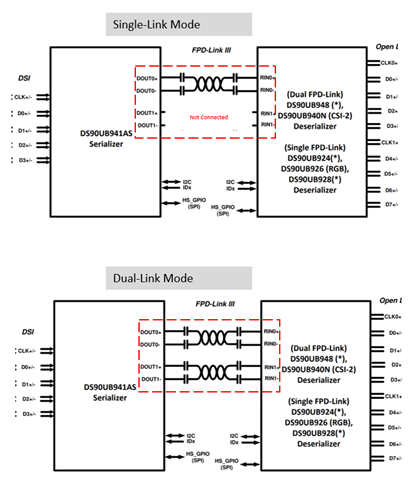

We are using DS90UB941AS-Q1 on our samsung SOC to connect with a display which has DS90UH948 deserializer.

We are able to access(r/w) the serializer registers via i2c.

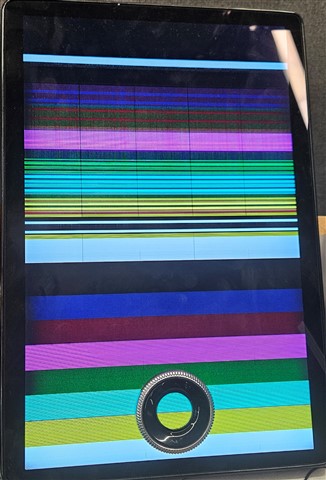

But the link detect with the deserializer fails.

What are the possible things which could cause link detect to fail?

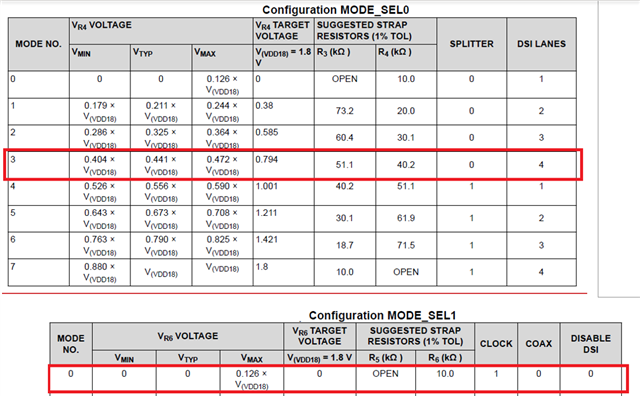

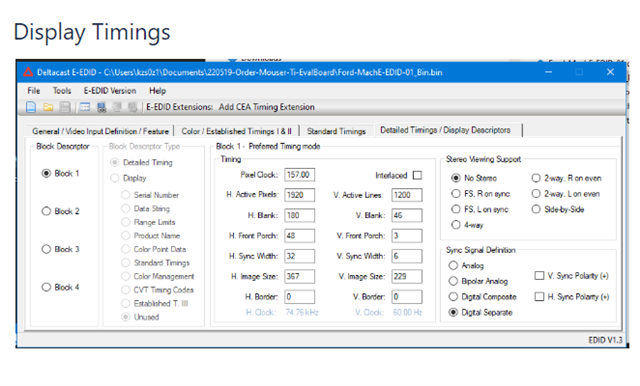

What are the settings which have to be checked/configured on the serializer side for this to work?