Other Parts Discussed in Thread: DS80PCI402, SN65DPHY440SS

Tool/software:

Hello, for the DS80PCI800 chip I have some questions, please answer, thank you!

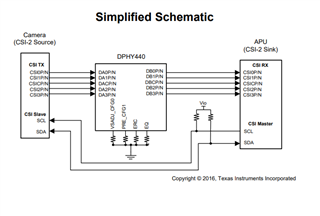

1. I would like to ask how to determine the chip DS80PCI800 is 4 lane, I understand that the lane is the same time, including TX and RX two sets of data, looked at some of the schematic design of this chip found that the input and output are generally TX or are RX, so there are some questions in this regard!

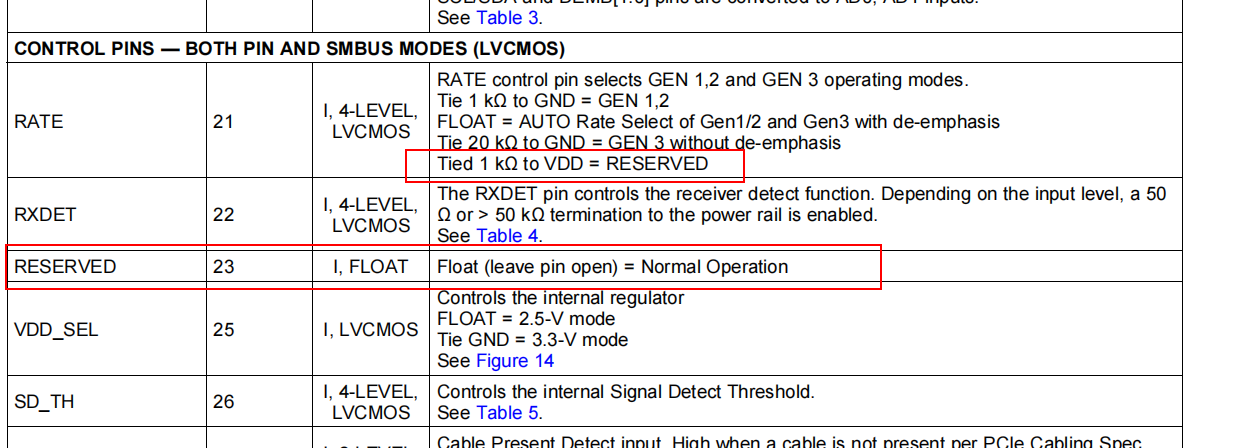

2. If you want to process the MIPI signal, how to determine whether it should be set to GEN1, GEN2 or GEN3

3. The chip's power supply mode has 3.3V and 2.5V, the selection of these two modes of reference standards?

4. Due to the design requirements, it may be necessary to use 5V voltage through the level conversion chip to get the required voltage, the level conversion chip specifications and PCB layout requirements?

Translated with DeepL.com (free version)