Part Number: SN65DP159

Tool/software:

Hi,

Please advise on the following customer inquiry.

Question)

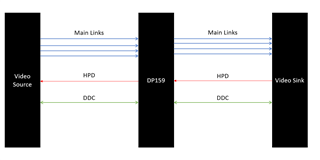

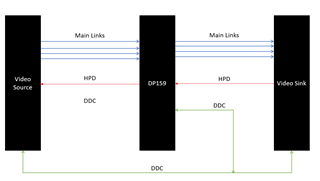

Is it possible to stop the video signal output of the retimer IC (SN65DP159) while the video signal is being input from the host to the retimer IC?

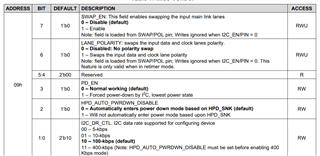

- Will the above operation be achieved by setting bit 0 (TMDS_OE) of register address 0x20h to "1"?

- Can we assume that DDC communication between the host and display remains possible even when bit 0 (TMDS_OE) of register address 0x20h is set to "1"?

Best regards,

Hiroshi