Other Parts Discussed in Thread: HD3SS3220, , DS160PR421, SN75LVPE5412

Tool/software:

These are my first steps in this type of circuits and I would really appreciate the opinion of an expert:

The big caption:

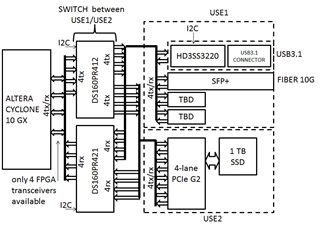

I'm using a ALTERA CYCLONE 10 GX FPGA, and I need to multiplex 4 FPGA transceivers (12.5 Gbps capable) in two applications to be dynamically selected:

> In USE1, the four transceivers will support a short range connection to a Solid State disk, using a 4-lane PCIe Gen2 interface at 5Gbps.

> In USE2, the four transceivers will be assigned to support one USB3.1 port, one SFP+10G optical link, and two inter-board links (still TBD). For the USB 3.1 front end, I selected TI's HD3SS3220 10-Gbps USB 3.1 Type-C 2:1 mux with DRP Controller.

Now, my question:

As for the quad 2:1 mux/demux to put between the HD3SS3220 and the FPGA, I have planned to use the TI's DS160PR412/421 pair to switch and redrive between 4-lane PCIe (in USE 1), and USB 3.1 plus SFP+ plus 2TBD (in USE 2). Since the DS160PR412/421 and the HD3SS3220 gain and EQ behavior can be dynamically programmed via I2C I assumed that the above set could be used for this purpose.

Is this correct, am I missing some essential thing or am I making a big mistake?

Thank you very much

Guillermo