Tool/software:

Hello Expert,

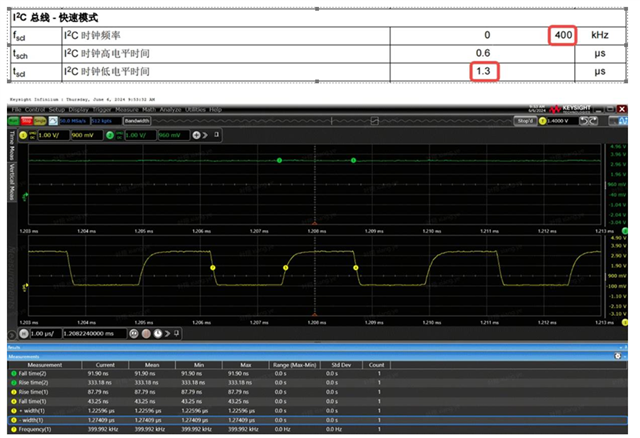

My customer tests IIC bus related parameters and found that the SCL low time does not meet the criteria of a slave for TCAL9539-Q1. The JACINTO, TDA4 SOC comes with a sdk or kernel drive set to 50% duty cycle of the IIC. SCL low is 1/(400K*2)=1.25us. This does not meet the minimum 1.3 us requirement. What is the risk if this parameter standard is not met? Does it risk to modify the associated high and low time register values in the self-contained drive code if the requirement is met without frequency reduction accepted? Or is there a risk of modifying the value of the associated high-low time registers in the user application code after the own drive configuration is complete?

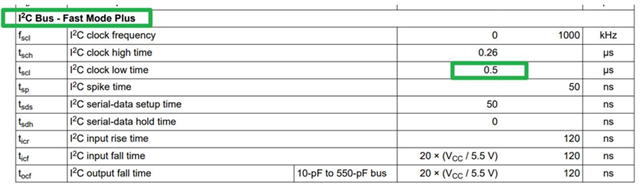

The customer can not use FAST MODE PLUS, because this mode needs 1.8V power supply and my customer's hardware is fixed. even the frequency can be 1MHZ, SCL low is 1/(1M*2)=0.5us, there is no margin as well.

Best regards,

Wenting