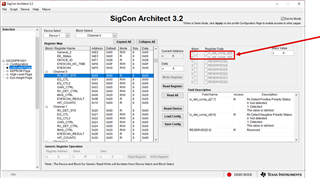

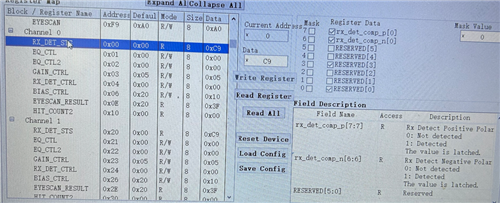

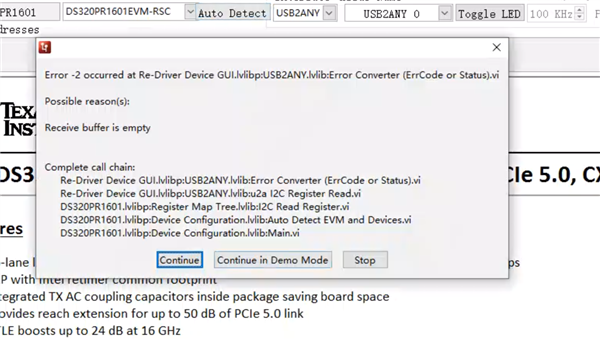

Part Number: DS160PR1601

Other Parts Discussed in Thread: DS320PR1601, , USB2ANY

Tool/software:

Hi,Experts

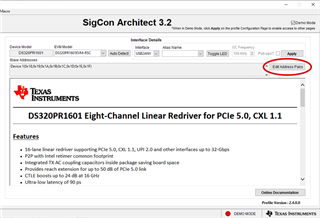

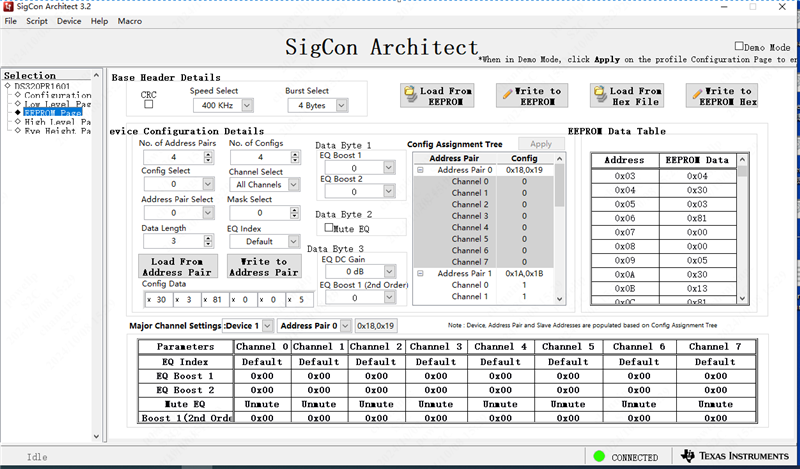

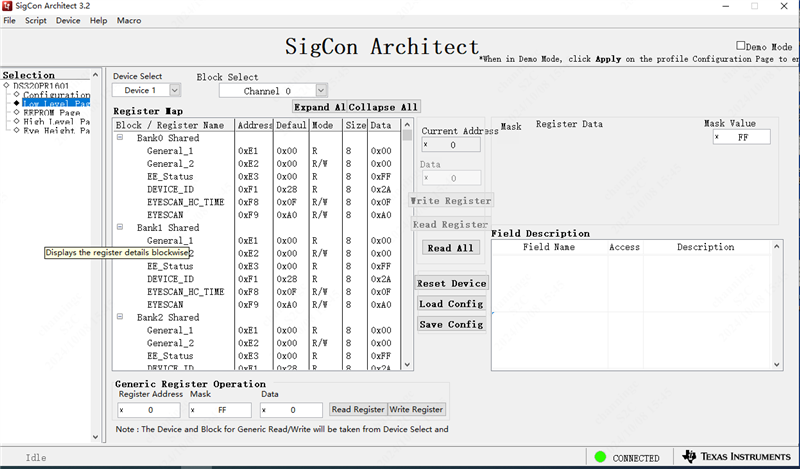

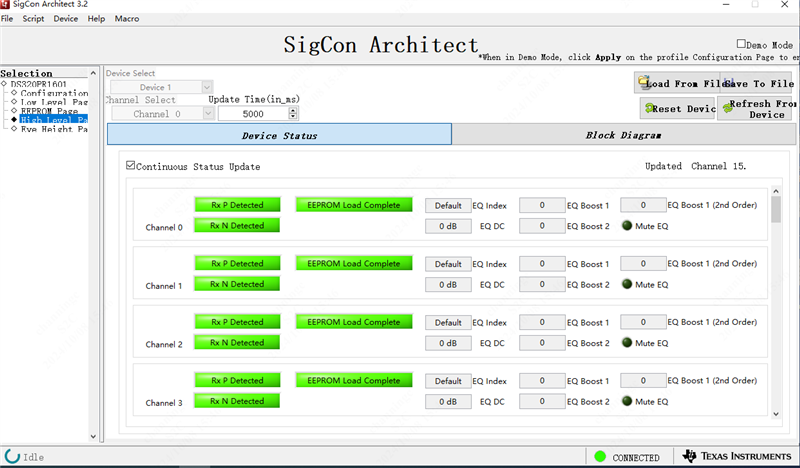

I use the SigCon Architect profile for the DS320PR1601 in order to configure DS160PR1601. When I connect the DS160PR1601, the SigCon Architect will report a Error like below:

Could you give me some advices to resolve this issue ?

Thanks

Powell