Tool/software:

Hi,

I am transmitting data to TLK6002 board from my customized FPGA board and doing shallow loopback and sendback same data to FPGA borad, in FPGA board sometimes receive clock locking is not happening.

But TLK6002 channel sync happened properly.

While I am configured tx clock, tx data, rx clock & rx data with HSTL logic it is happened but when I configured these signals with LVCMOS rx clock is locking properly.

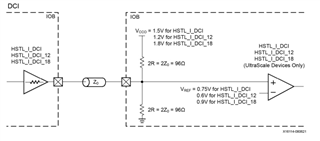

As per my understanding there is no need of termination resistors for LVCMOS logic but in HSTL logic we have to maintain termination resistors.

In above figure: Output means TLK6002 generated output impedance?. based on this how much impedance I have to configure in FPGA ip.

From FPGA output how much output impedance I have to provide.

Thanks & Regards,

Mallikarjuna.