Tool/software:

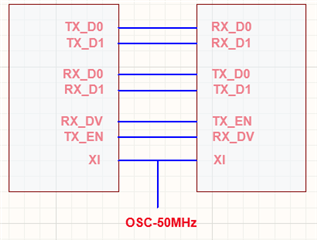

We are currently working on a design for which we want to use a DP83825I in repeater mode to conect via RMII to another controller that acts as a PHY (a Valens VS3000).

We have designed and produced an experimental board, with which we connected a PC to the DP83825I via Ethernet and sent continuos pings to test. The link is detected and the DP83825I is receiving the PING packets, but the other chip marks them as incorrect. Checking with an oscilloscope we are seeing that the RX_DV signal is getting fired sooner than expected and is getting released also sooner than expected. See below the RX_DV signal (Red channel) with RX_D0 signal (Blue channel).

We checked with a wortking Ethernet design the same lines to see how they should look. See below the RX_DV signal (Blue channel) with RX_D0 signal (Red channel)

We are at a loss on what is happening here. We tried to artificially increment the lenght of the RX_DV trace to see if it can be delayed but doubling the distance (so it ends up being the largest line) just shaved around 5 ns out of 130 ns.

We also tried connecting two DP83825I in repeater mode as stated in the datasheet to test with a pure repeater and we got the same readings.

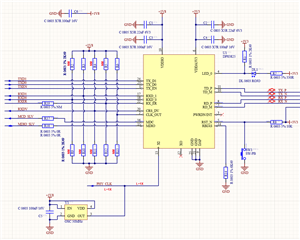

The schematics of the DP8325I part for both tests is as follows (NM is the same as DNP):

Any ideas on what is wrong for this to happen?

Thank you and best regards,