Part Number: DP83867IS

Tool/software:

Hi,

During the power-on sequence, Before supplying VDDIO (1.8V) for the DP83867ISRGZR. We plan to supply the stable LVCMOS1V8 25MHz +/-50ppm clock from an on-board oscillator. However, VDD1P0 (1V) and VDDA2P5 (2.5V) will be applied before the clock starts to toggle.

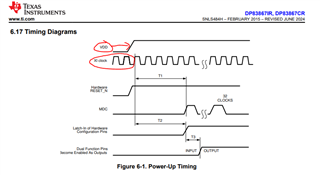

Does this momentary hot-socketing during the power-on sequence is allowed? As per the "Figure 6-1. Power-Up Timing" of the Datasheet we believe it is supported.

Also, we believe, our two supply schemes wouldn't need any sequencing between rails.

Kindly confirm the above queries at the earliest.