Part Number: SN65DSI86

Tool/software:

What criteria does the SN65DSI86 use to determine and report whether the link clock and stream clock are asynchronous or synchronous?

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

Part Number: SN65DSI86

Tool/software:

What criteria does the SN65DSI86 use to determine and report whether the link clock and stream clock are asynchronous or synchronous?

Hi Augusto,

The link clock and stream clock will be synchronous if the DSI stream is used to clock the eDP output. If the REFCLK is used, then this is an asynchronous stream.

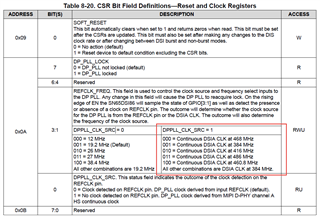

Thank you for clarifying. We have a situation were the refclk_freq is configured as DSIA CLK at 486Mhz and register 0x0A is reporting (0x0A = 0x87) as expected.

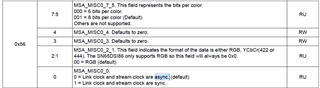

However, register 0x56 is reporting 0x20 which indicates "Async". We expected this to report "Sync" given the reference clock is configured for DSIA CLK. The display port MSA data is also reporting "Async".

Do you have any suggestions or possible explanation for this unexpected behavior?

Interesting, I will have a conversation with a systems engineer on this part and I will get back to you tomorrow. I agree this is unexpected behavior.

Hi Vishesh,

Have you been able to obtain any feedback on the unexpected DSIA CLK response we are experiencing? Any insight would be greatly appreciated.

Hi Augusto, Unfortunately the designers that built this chip have since left TI.

The team and I have been looking into the verilog files for the digital eDP section but we don't have any insights as of yet. Is the MSA being ASYNC affecting the signal integrity/ functionality of the part?

Hi Augusto,

After looking at the Verilog file I have found the reason the stream is asynchronous.

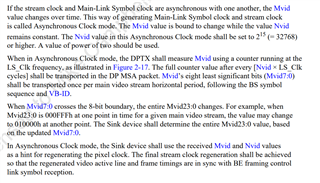

As per the DP spec we know that if the link clock and stream clock are derived from the same source then the stream is synchronous. In a synchrnous stream the ratio of Nvid and Mvid is some hardcoded value based of off the data rates used.

In a asynchronous stream the Nvid is held at a constant value a a counter is incremented every clock cycle. This is implemented as follows.

This asynchronous Mvid and Nvid calculation can be used to generate Mvid and Nvid values for both synchronous and a synchronous streams. In our design we have implemented the asynchronous Mvid and Nvid calculation for both asynchronous and synchronous streams. This is why the MSA bit will always read asynchronous when using this device.

Interesting, I will have a conversation with a systems engineer on this part and I will get back to you tomorrow. I agree this is unexpected behavior.

I apologize for any confusion this statement provided. I was unaware of our design at that time.

Best,

Vishesh Pithadiya