Part Number: SN65DSI84-Q1

Other Parts Discussed in Thread: SN65DSI84

Tool/software:

Hi team,

Please clarify the following questions:

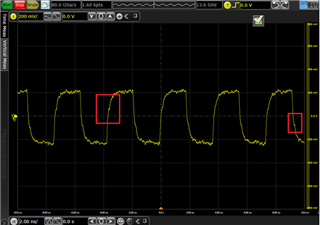

1. We see that there are some glitches on the rising and falling edges of the DSI CLK waveform (as shown in the red box in the figure below). Is there a filter or other related circuit inside the SN65DSI84-Q1 to eliminate the impact of this glitches?

Will these glitches affect the sampling of the SN65DSI84-Q1?

2. We see the simulation waveform of SN65DSI84 on TI's official website, but its package is different from that of SN65DSI84-Q1 (not sure what other differences there are).

Can I use the simulation model of SN65DSI84 in the link below to simulate the signal integrity of SN65DSI84-Q1?

https://www.ti.com.cn/product/cn/SN65DSI84#design-tools-simulation