Other Parts Discussed in Thread: LMK1D2102

Tool/software:

Hello,

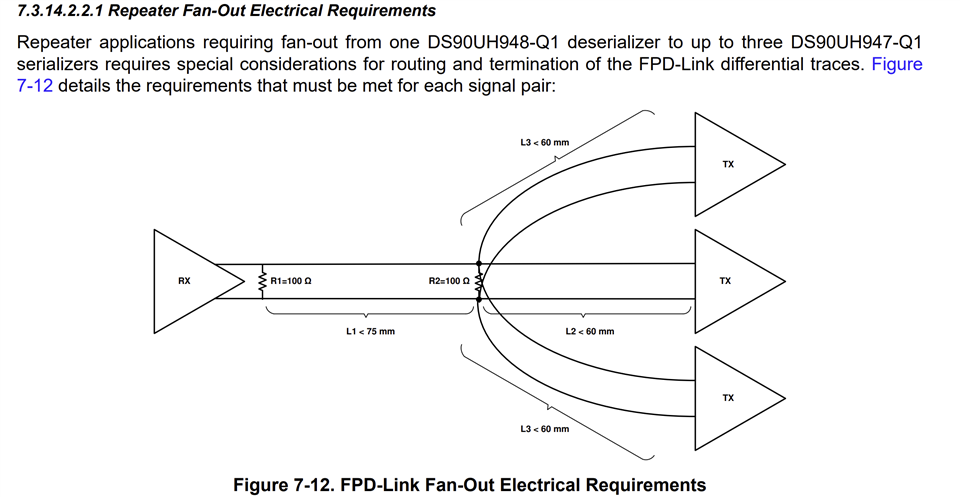

We are designing device which should implement HDCP repeater mode according to Figure 7-12, p.38 in datasheet. But concerning about signal integrity issues in such configuration. To check this we performed simple simulation for setup/configuration from Figure 7-12, and got quite bad results even at low LVDS speeds (100 - 200MHz for single LVDS pair). While point-to-point setup works quite well. We used DS90UH947 at the receiver side.

The question is: will HDCP repeater configuration work, if we insert fan-out buffer between DS90UH948 and DS90UH947? Something like LMK1D2102 or similar.

Best regards, Aleksandr