Tool/software:

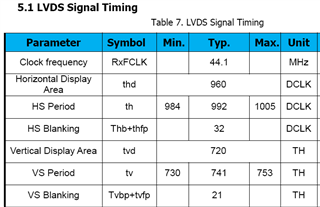

We have a scenario where the UB948 deserializer is connected to an oLDI 2 channel 1920x720 display, so the horizontal data is split into even/odd 960 pixels. The display has the following parameters:

Question: when setting up a test pattern generator on the UB949 serializer - the clock frequency and the horizontal period has to be doubled? The serializer will then split the data into even and odd pixels itself? Could I kindly request that you could write a patgen test script for such screen? The UB949/UB948 pair uses dual-link connection. Thank you.