Other Parts Discussed in Thread: ALP, USB2ANY

Tool/software:

Hi Teams,

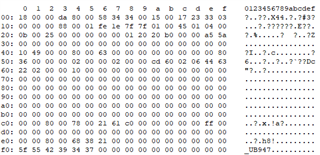

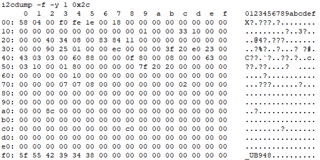

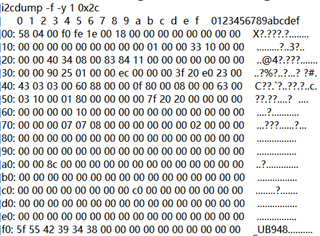

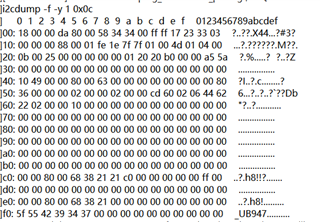

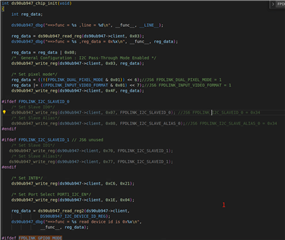

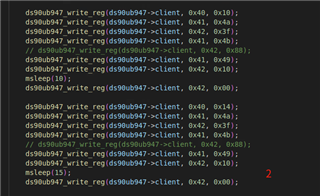

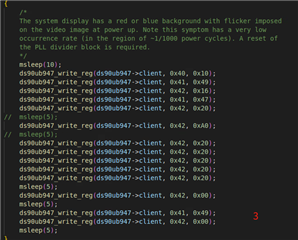

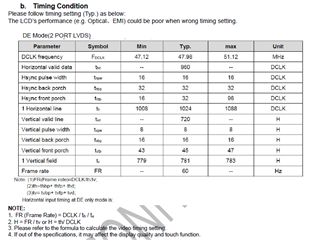

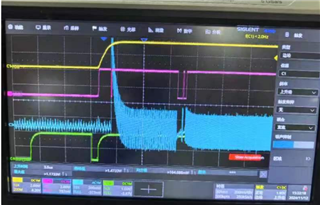

We bulided a new solution with 947/948, sometimes the screen display would shaking, we dump the 947/948 registers map.

And we compared them with correct module, we found the NG module's 948 register 0x3B = 0x00, the OK module is 0x3F,

so what's the meaning of 0x3B(EQ status)