Part Number: TIC12400-Q1

Other Parts Discussed in Thread: TIC12400, , TIC10024-Q1

Tool/software:

Hi team,

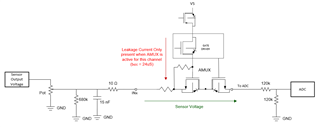

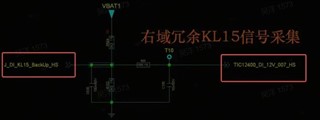

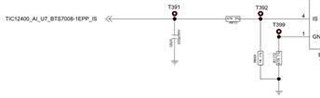

We met a problem on using ADC input mode of TIC12400. The input of IN11 is analog signal. You can find the circuit of input side as below.

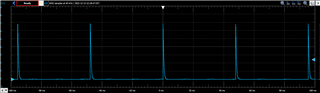

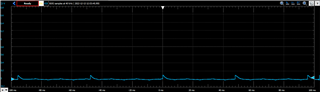

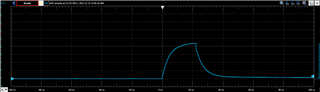

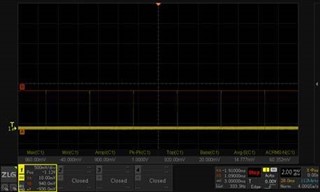

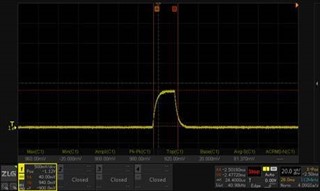

They are using ADC polling mode, the wetting current is configured to 0mA. But they captured an abnormal periodic pulse at IN11. You can find the waveform as below.

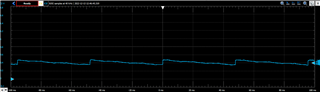

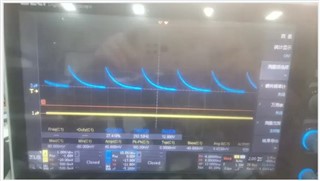

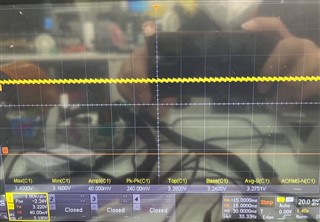

I suspect that it is cause by IIN_LEAK_0mA. After placing a 15nF cap at IN11, the voltage level get worse, see below. Please help provide some suggestions to debug.

Schematic as below.

Thanks!

Ethan Wen